Emergence, Complexity and Computation

# Ioannis Vourkas Georgios Ch. Sirakoulis

# Memristor-Based Nanoelectronic Computing Circuits and Architectures

Foreword by Leon Chua

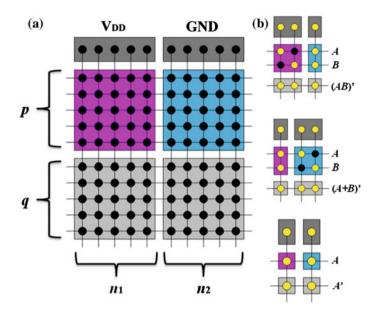

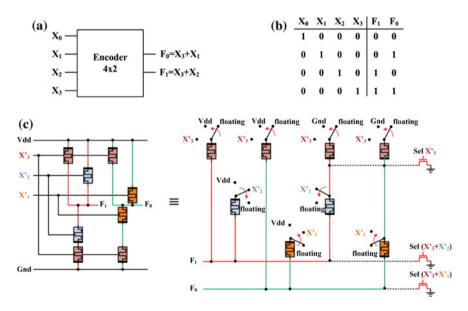

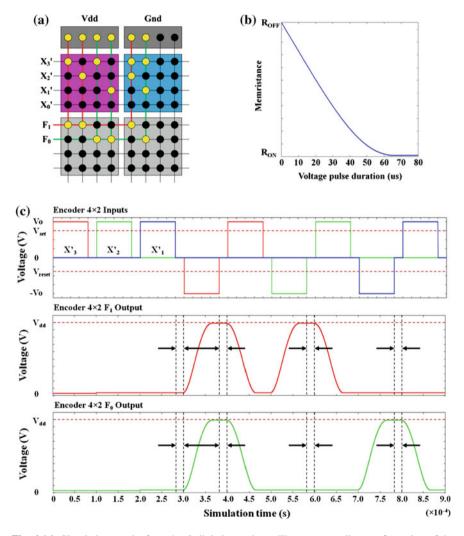

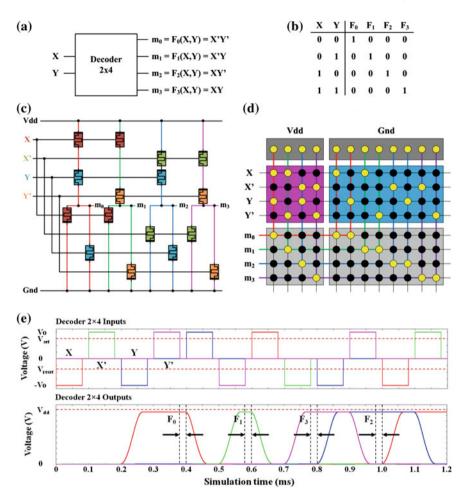

# **Emergence, Complexity and Computation**

Volume 19

#### Series editors

Ivan Zelinka, Technical University of Ostrava, Ostrava, Czech Republic e-mail: ivan.zelinka@vsb.cz

Andrew Adamatzky, University of the West of England, Bristol, UK e-mail: adamatzky@gmail.com

Guanrong Chen, City University of Hong Kong, Hong Kong, China e-mail: eegchen@cityu.edu.hk

#### **Editorial Board**

Ajith Abraham, MirLabs, USA Ana Lucia C. Bazzan, Universidade Federal do Rio Grande do Sul, Porto Alegre, RS, Brazil Juan C. Burguillo, University of Vigo, Spain Sergej Čelikovský, Academy of Sciences of the Czech Republic, Czech Republic Mohammed Chadli, University of Jules Verne, France Emilio Corchado, University of Salamanca, Spain Donald Davendra, Technical University of Ostrava, Czech Republic Andrew Ilachinski, Center for Naval Analyses, USA Jouni Lampinen, University of Vaasa, Finland Martin Middendorf, University of Leipzig, Germany Edward Ott, University of Maryland, USA Lingiang Pan, Huazhong University of Science and Technology, Wuhan, China Gheorghe Păun, Romanian Academy, Bucharest, Romania Hendrik Richter, HTWK Leipzig University of Applied Sciences, Germany Juan A. Rodriguez-Aguilar, IIIA-CSIC, Spain Otto Rössler, Institute of Physical and Theoretical Chemistry, Tübingen, Germany Vaclav Snasel, Technical University of Ostrava, Czech Republic Ivo Vondrák, Technical University of Ostrava, Czech Republic Hector Zenil, Karolinska Institute, Sweden

المنسارات

#### About this Series

The Emergence, Complexity and Computation (ECC) series publishes new developments, advancements and selected topics in the fields of complexity, computation and emergence. The series focuses on all aspects of reality-based computation approaches from an interdisciplinary point of view especially from applied sciences, biology, physics, or chemistry. It presents new ideas and interdisciplinary insight on the mutual intersection of subareas of computation, complexity and emergence and its impact and limits to any computing based on physical limits (thermodynamic and quantum limits, Bremermann's limit, Seth Lloyd limits...) as well as algorithmic limits (Gödel's proof and its impact on calculation, algorithmic complexity, the Chaitin's Omega number and Kolmogorov complexity, non-traditional calculations like Turing machine process and its consequences,...) and limitations arising in artificial intelligence field. The topics are (but not limited to) membrane computing, DNA computing, immune computing, quantum computing, swarm computing, analogic computing, chaos computing and computing on the edge of chaos, computational aspects of dynamics of complex systems (systems with self-organization, multiagent systems, cellular automata, artificial life,...), emergence of complex systems and its computational aspects, and agent based computation. The main aim of this series it to discuss the above mentioned topics from an interdisciplinary point of view and present new ideas coming from mutual intersection of classical as well as modern methods of computation. Within the scope of the series are monographs, lecture notes, selected contributions from specialized conferences and workshops, special contribution from international experts.

More information about this series at http://www.springer.com/series/10624

المنسارات

# Memristor-Based Nanoelectronic Computing Circuits and Architectures

Ioannis Vourkas Department of Electrical and Computer Engineering Democritus University of Thrace Xanthi Greece Georgios Ch. Sirakoulis Department of Electrical and Computer Engineering Democritus University of Thrace Xanthi Greece

ISSN 2194-7287

ISSN 2194-7295

(electronic)

Emergence, Complexity and Computation

ISBN 978-3-319-22646-0

ISBN 978-3-319-22647-7

(eBook)

DOI 10.1007/978-3-319-22647-7

Library of Congress Control Number: 2015946759

Springer Cham Heidelberg New York Dordrecht London © Springer International Publishing Switzerland 2016

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer International Publishing AG Switzerland is part of Springer Science+Business Media (www.springer.com)

to my wife Evelyn with love I.V. to my family: Stella, Marina, and Christos for their love and support G.S.

المنارات

# Foreword

The memory-resistor (memristor) is a two-terminal electronic device, defined by a state-dependent Ohm's law; its resistance depends on a set of internal state-variables. The favorable circuit properties of memristors justify the recent explosive growth of related research efforts which led to several advancements in theory and potential unique applications of memristors including, among others, computing.

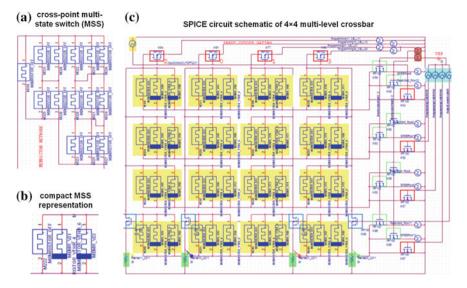

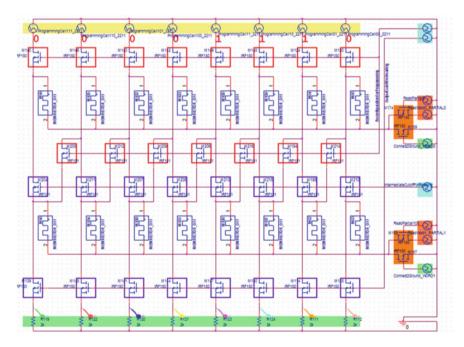

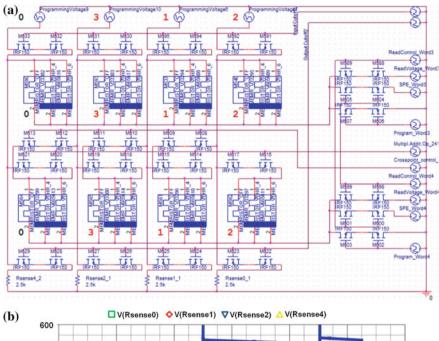

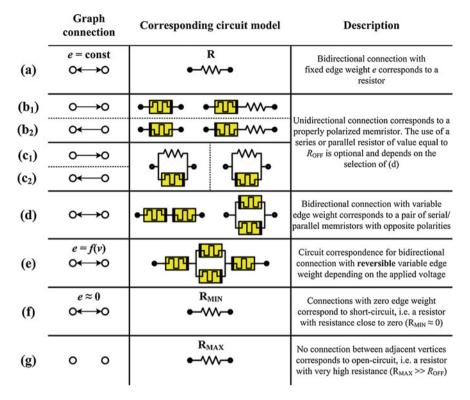

Currently there are only a few available book titles devoted to memristors. Vourkas and Sirakoulis in Memristor-Based Nanoelectronic Computing Circuits and Architectures bring together a series of memristor-related topics which are studied and presented for the first time in a single volume, i.e. device modeling, complex device interconnections, logic and memory circuits, as well as computing circuits and systems where the memristors are used either as two-state switches or as analog devices. More specifically, the book consists of eight main chapters. Chapter 1 deals with the foundations of memristor theory and the fundamental properties of memristors. Chapter 2 is devoted to modeling of voltage-controlled bipolar memristors and describes a threshold-type SPICE-compatible device model, on which the authors based the simulations and research findings shown in the rest of the book. Chapter 3 focuses on complex memristor interconnections and studies the composite emerging behavior with application in memristive multi-state switches. Chapter 4 addresses design strategies for digital logic circuits with memristors, passing from sequential stateful logic to new circuit design schemes which allow for parallel processing of the applied inputs. Chapter 5 is dedicated to crossbar-based information storage systems, studying alternative memory cells and architectural aspects which could lead to more reliable memristor memories. In the same context, Chapter 6 integrates the memristive multi-state switches of Chap. 3 with the crossbar circuit geometry in a multi-level memristor-based crossbar memory, which is then used in an early approach to memristor-based high-radix arithmetic logic units (ALU). Chapter 7 studies the emerging parallel computing capabilities of complex two-dimensional memristor networks and presents a novel methodology to efficiently map oriented graphs onto memristive networks, using

circuit models which cover a variety of connection types between graph vertices. Finally, Chapter 8 presents a circuit-level Cellular Automata (CA)-inspired methodology for computational schemes which are applied to solve several NP-hard problems of various areas of artificial intelligence (AI).

All the parts of the book are written in a simple language accessible by scientists, researchers, engineers, as well as young undergraduates. This book title is unique and timely, providing a comprehensive study which spans from memristor fundamental theory, device modeling and device interconnections, to circuit-level and system-level digital/analog applications. It includes several new results originating from the research endeavor of the authors in this very promising and highly multidisciplinary scientific field. At the moment, there is not any competitive title which deals with the range of the provided here memristor-related research in a truly compact form, which is why *Memristor-Based Nanoelectronic Computing Circuits and Architectures* can be a valuable textbook for undergraduate and postgraduate students.

Berkeley, USA

Leon Chua

المسلك للاستشارات

# Preface

# Motivation

Continued dimensional and functional scaling of Complementary Metal-Oxide-Semiconductor (CMOS) technology is driving information processing into a broadening spectrum of new applications. Many of these applications are enabled by performance gains and/or increased complexity realized by scaling. The performance of the components and the final application can be measured in many different ways; higher speed, higher density, lower power, more functionality, etc. Traditionally, though, dimensional scaling had been adequate to bring about these performance merits but it is no longer so. Since dimensional scaling of CMOS will eventually approach fundamental limits, several new alternative information processing devices and architectures for existing or new functions are being explored to sustain the historical integrated circuit scaling cadence and the reduction of cost/function in the next decades [1].

CMOS logic and memory together form the predominant majority of semiconductor device production. Today the semiconductor industry is facing two classes of difficult challenges related to extending integrated circuit technology to new applications and to beyond the end of CMOS dimensional scaling. One class relates to pushing CMOS beyond its ultimate density and functionality by integrating a new high-speed, highly-dense, and low-power memory technology onto the CMOS platform. The other class is to extend information processing substantially beyond that attainable by CMOS, using an innovative combination of new devices, interconnect and architectural approaches for extending CMOS and eventually inventing a new information processing platform technology. Difficult challenges gating the development of emerging research devices are therefore divided into two parts: (i) those related to memory technologies, and (ii) those related to information processing or logic devices.

المستشارات

The semiconductor industry is definitely in need of a new memory technology that combines the best features of current memories in a fabrication technology compatible with the CMOS process flow, scaled beyond the present limits of SRAM and Flash. This would provide a memory device fabrication technology required for both stand-alone and embedded memory applications. For DRAM, currently the main goal is to continue to scale the foot-print of the 1T-1C cell to the practical limit of  $4F^2$ , where F is the minimum feature size. Some issues concern vertical transistors, new dielectrics which improve the capacitance density, and keeping the leakage currents low. The requirement of low leakage currents, however, causes problems in obtaining the desired access transistor performance. A revolutionary solution of having a capacitor-less cell would be highly beneficial. Regarding nonvolatile memory (NVM), the current mainstream is Flash memory. Dense, fast, and low-power NVM is becoming highly desirable in computer architecture. However, there are serious issues with scaling of Flash memories. 2D Nand-type Flash should stay dominant for as far as it can scale because it is a well-established technology and has a very simple structure, requiring only one transistor. Ultimate density scaling may require 3-D architecture, such as vertically stackable cell arrays with acceptable yield and performance. 3-D Nand Flash is currently being developed but cost-effective implementation of this new technology, along with multi-level cell and acceptable reliability, remains a difficult challenge. Consequently, since the ultimate scaling limitation for charge-based storage devices is too few electrons, devices that provide memory states without electric charges are promising to scale further.

Moreover, as mentioned before, a major portion of semiconductor device production is devoted to CMOS digital logic, both high-performance and low-power, which is typically for mobile applications. A longer-term challenge is therefore the invention of a producible information processing technology addressing "beyond CMOS" applications. For example, emerging research devices might be used to realize special purpose processing units that could be integrated with multiple CMOS components to obtain performance advantages. These new special purpose units may provide a particular system function much more efficiently than a digital CMOS block, or they may offer a uniquely new function not available in a CMOS-based approach. A new information processing technology must also be compatible with a system architecture that can fully utilize the new device. Possibly, a non-binary data representation and/or non-Boolean logic may be required to employ a new primitive device for information processing.

All aforementioned requirements are currently driving the industry towards a number of major technological innovations, including material and process changes, as well as totally new circuit structures. There is a growing interest in new devices for information processing and memory, new technologies and new paradigms for system architecture. Solutions to all these challenges could also lead to

المسلك للاستشارات

new opportunities for an emerging research device technology to eventually replace CMOS as a mainstream information processing technology, provided that it possesses most of (if not all) the mentioned desirable performance merits. To this end, resistive-switching devices known as "memristors" or "memristive devices" have become the focus of many research efforts by academia and industry lately. Their advantageous performance characteristics render them a candidate technology able to bring the next technological revolution in electronics, while serving as a bridge between CMOS and the realm of nanoelectronics beyond the end of CMOS dimensional and equivalent functional scaling.

# **Memristor: A Promising Emerging Nanoelectronic Device**

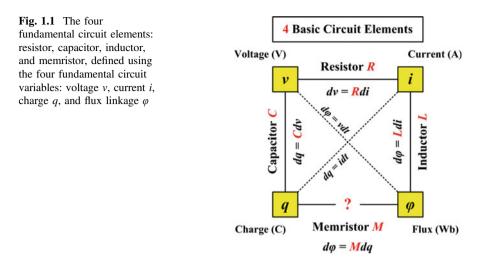

As a result of his preliminary exceptional work in nonlinear circuit theory during the 1960s, in 1971 Prof. L.O. Chua made an interesting observation that led to his discovery of the memristor as a mathematical entity [2]. For completely linear circuits there are only three independent two-terminal passive circuit elements: the resistor R, the capacitor C, and the inductor L, which are defined axiomatically via a constitutive relation between a pair of variables chosen from {v (voltage), i (current), q (charge),  $\varphi$  (flux linkage)}. There are six different pairs than can be formed from these four variables, namely { $(v, \varphi), (i, q), (v, i), (v, q), (i, \varphi), (\varphi, q)$ }, and five of them were already related mathematically. However, when Chua generalized the mathematical equations to be nonlinear, there was another independent differential relationship that in principle coupled the charge q that flowed through the circuit and the *flux linkage* (time-integral of the applied voltage)  $\varphi$  as in  $d\varphi = Mdq$ , different from the resistance which coupled the voltage v to the current i, dv = Rdi.

He mathematically explored the properties of this new nonlinear circuit element and found that it was essentially a "resistor with memory", so he called it a memristor M; it was a two-terminal device that changed its resistance according to the amount of change that flowed through it. This prediction of the properties of a new "missing" (by that time) circuit element from symmetry principles was absolutely revolutionary; more importantly, it did not depend on any experimental observation but it was rather a result of curiosity. As Chua himself declared in his 1971 paper, it was not obvious at that time that a physical analog of such circuit element existed; the attached text below is a summary of what is stressed in the original paper (last paragraph on page 519 of [2]).

Although no physical memristor has yet been discovered, the circuit-theoretic and quasi-static electromagnetic analyses presented make plausible the notion that a memristor device could be invented, if not discovered accidentally! It is perhaps not unreasonable to suppose that fabricated as a laboratory curiosity but was fabricated as a laboratory curiosity but was

The reason why memristors are substantially different from the other fundamental circuit elements is that, when you turn off the voltage to the circuit they still remember how much voltage was applied before and for how long, thus presenting a memory of their past. That's an effect that can't be duplicated by any circuit combination of resistors, capacitors, and inductors, which qualifies the memristor as a fundamental circuit element.

Today we know that memristors are ubiquitous and many devices, including the "electric arc" which dates back to 1801, have been identified as memristors. Indeed, there had been experimental clues to the memristor's existence all along the last two centuries. Scientists have been publishing in the literature experimental results with "strange" voltage characteristics, where one sees clearly memristance, though such a material property had always been shadowed by other effects that were of primary interest [3]. In the absence of an application, there was no particular need to seek memristive behavior anyway. After the publication of Chua's seminal paper, the connection between many strangely behaving components and his original theoretical definition was not made at least for three decades by then. The memristor had been relegated as an abstract device with no practical significance until 2008 when Chua's theory of memristor was successfully linked to its first "modern" practical nanoscale implementation by a group at Hewlett Packard (HP) Laboratories [4]. Their seminal Nature paper originated intense research activity in this novel scientific field and generated unprecedented worldwide interest for the potential applications, with publications increasing at an exponential rate ever since.

Memristor exhibits its unique properties primarily at the nanoscale. Therefore, much of the recent research work has focused on the technological side concerning

the physical realization of such devices for a better understanding of the physical principles and their tuning. Currently, there is a growing variety of systems that exhibit memristive behavior, as academia and industry keep on with their research and prototyping [5, 6]. Among them, molecular and ionic thin film memristive systems primarily rely on different material properties of thin film atomic lattices that exhibit hysteresis under the application of charge. In experimentally realizable systems, memristive devices with threshold voltages seem to be the norm rather than the exception, and electronic conduction is in most cases dominated by an effective tunneling barrier—width that varies with the applied voltage.

The memristor creates a new opportunity for realization of innovative circuits that in some cases are not possible or have inefficient realization in the present and established design domain. It provides many advantages such as scalability down to sub-10 nm, nonvolatility, fast switching speed, energy efficiency, and CMOS compatibility, just to name a few; thus it is believed to bring a new wave of innovation in electronics, supplanting or supplementing transistors in several applications, while it might bring analog information processing back into the world of computing. Memristor-based circuits open new pathways for the exploration of advanced computing architectures as promising alternatives to conventional integrated circuit technologies, which are facing serious challenges related to continuous scaling [1]. Most importantly, memristors provide an unconventional computation framework, different from familiar paradigms, which combines information processing and storage in the memory itself; i.e. the major distinction from the present day's computing technology [7]. Such framework is determined more by the device properties than any previously conceived logic paradigm.

Amongst several emergent applications of the memristance switching phenomenon, implementation of logic circuits is gaining considerable attention. In binary digital circuits, memristors would operate as two-state switches, toggling between max and min resistance. Using memristors for digital processing has the advantage of combining storage and logic functionality with the same technology in one single device. However, the widest field of proposals on how to use memristors for processing concerns analog computing. If several intermediate resistive states could be distinguished reliably, then the information density could be raised to more than one bit per device, but the end point of this evolution is to be able to fully exploit the analog nature of memristors. For example, using the possibility to store a ternary value in one physical storage cell allows building up a better arithmetic unit as is fundamentally possible and actually done with conventional binary logic. Anyway, active components such as transistors would still be needed even if most information processing were done by memristors. One reason is that signals are reduced in amplitude by every passive circuit element and, at some point, they must be restored. Another reason might concern accessing memristors for reading/programming their state. Hybrid circuits that combine memristors and active elements are a lively area of investigation, whereas the distinct properties of memristive devices might even lead to neuromorphic computer systems in the future [8].

Up to now, the fabrication of digital memories is the driving force of memristor technology, since very dense memory architectures can potentially be manufactured. Rapid progress in the advancements of memristive technology is reflected in the early commercialization of memristive memory (resistive RAM-ReRAM) products [9]. Such activity together with the groundbreaking announcement of "the Machine" by HP on June 2014 [10], prove the ever-increasing interest and active involvement of industry leading companies in the future production of memristor-related products and pioneering memristive computing architectures. The continuous improvement of the memristance switching behavior, thanks to the incessant accumulation of knowledge on resistive switching materials and the underlying phenomena, is encouraging for the future implementation and establishment of unconventional computing paradigms and sophisticated memristive circuits and systems. But whether the memristor will finally fulfill all these hopes remains to be seen; in order to evaluate long-term prospects of such technologies one would have to go beyond the basic principles and to questions of reliability, variability, manufacturing cost, etc.

The content of this book spans from fundamental device modeling to emerging storage system architectures and novel circuit design methodologies, targeting advanced non-conventional analog/digital massively parallel computational structures. Effective modeling is the first step towards a deeper understanding of the memristive dynamics and the better exploitation of their unique properties for potential utilization in a variety of emerging applications. Well defined and effective SPICE-compatible memristor models, as those presented in Chap. 2, would certainly accelerate research in memristive circuits and systems. Also, while most of the research has so far focused on the properties of single memristors, very little is known about their response when they are organized into networks. Composite memristive systems built out of networks of individual memristors, demonstrate different electrical characteristics from their structural elements due to their threshold-dependent nonlinear resistance switching behavior. Therefore, their rich and dynamic overall behavior could be exploited for the creation of novel sophisticated memristive circuits and systems with multi-bit storage per device capabilities. Collective memristive dynamics is the focus of Chaps. 3, 7, and 8, whereas the same property is the basis for the design of memristor-based logic circuits in Chap. 4. Furthermore, nonvolatile resistive RAM (ReRAM) is nowadays considered as one of the promising alternatives to current baseline memory technologies. At the architectural level, crossbar memory cell array structure offers several benefits and is considered one of the best ways to implement ReRAM of highest possible device density. However, a typical passive crossbar memory suffers from the existence of parasitic conducting (current sneak paths) reducing both the size and the reliability of the memory. Innovative approaches to memory cell structure and memory architecture, which will efficiently address the current sneak-path problem, constitute nowadays a key factor towards the practical realization of passive crossbar-based ReRAM and reflect the content of Chap. 5.

Preface

Moreover, a great effort was placed towards the creation of relevant design automation/simulation tools and proper methodologies which address important current technological drawbacks and thus enable/facilitate the development of efficient design flows for reliable circuits and architectures comprising memristors. Such tools are presented in Chaps. 4 and 5. Furthermore, it has been well-known for a long time that faster arithmetic operations could be achieved via high-radix numeric systems [11]. However, in the absence of appropriate storage devices, such practice was not given much attention because it would require doubling the memory capacity to represent high-radix numbers in binary mode. In Chap. 6 we present a novel method for implementing crossbar-based multi-level memories, where each cross-point cell stores multiple bits. Furthermore, we propose a conceptual solution for novel CMOS-compatible, memristive, high-radix arithmetic logic units (ALUs) for future computing systems.

The extensive study of memristive nanoelectronic circuits and architectures presented within this book is indicative of the fast pace of this novel and intriguing field. High-density memristive data storage combined with memristive circuit-design paradigms and computational tools applied to solve NP-hard artificial intelligence (AI) problems, as well as memristive arithmetic-logic units, certainly pave the way for a much promising memristive era in electronic computing systems. The graph-based NP-hard problems are depicted to memristive networks and coupled with Cellular Automata (CA)-inspired computational schemes that enable computation within memory. The following chapters may constitute an informative cornerstone for researchers and scientists, as well as a comprehensive reference to the more experienced readers, hoping to stimulate further research on memristive devices, circuits, and systems.

#### **Book Outline**

Below there is a short summary of the following chapters which highlights the original contributions of this book to the *state-of-the-art*.

Basic theoretical definitions and general properties of memristors and memristive systems are shortly presented in Chap. 1. All necessary information for the purposes and the complete comprehension of the content of this book is provided.

In Chap. 2, the device characteristics of thin-film memristors are considered and a novel, SPICE-compatible, generic, threshold-type switching model of a two-terminal voltage-controlled bipolar memristor is presented, explaining the memristive behavior of the device by investigating the occurrence of quantum tunneling.

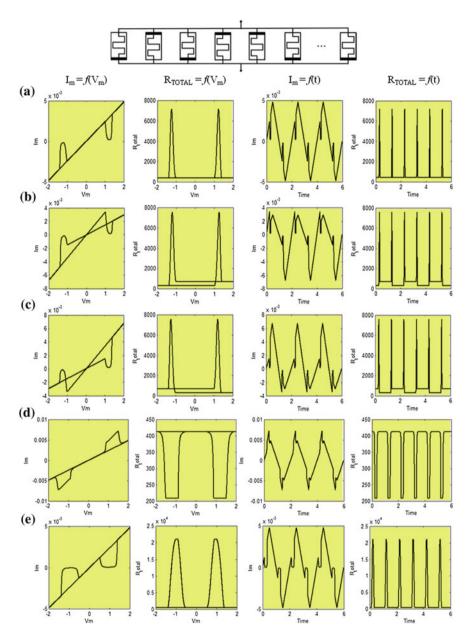

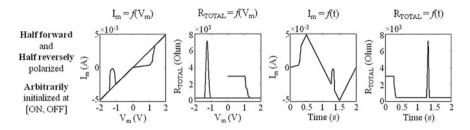

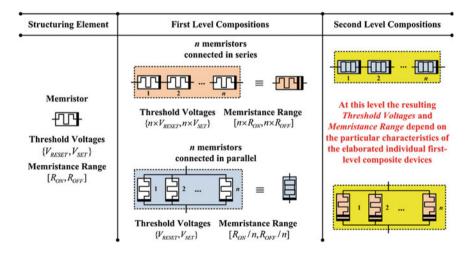

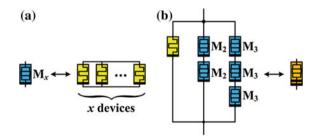

A rigorous study of the switching response of composite memristive systems, consisting of multiple memristors connected in complex circuit configurations, is presented in Chap. 3. A methodology for the construction of composite memristive devices, which comply with certain design specifications and facilitate the design of nanoelectronic circuits with multi-state switches, is presented. Particular application

examples of the methodology in novel analog computational structures conclude this chapter.

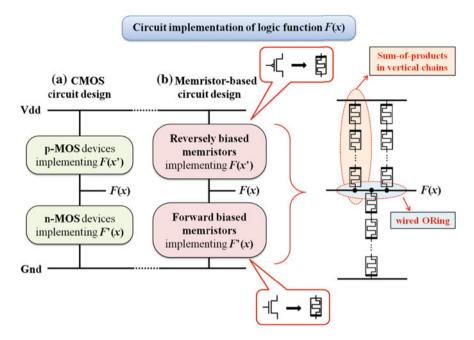

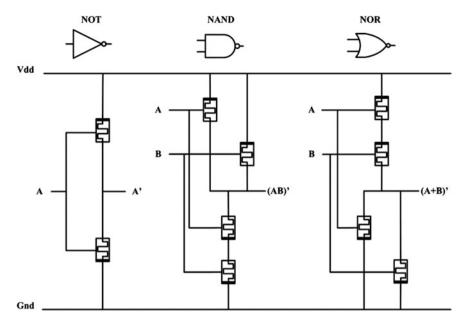

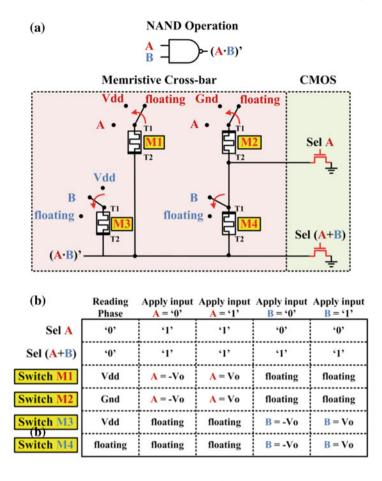

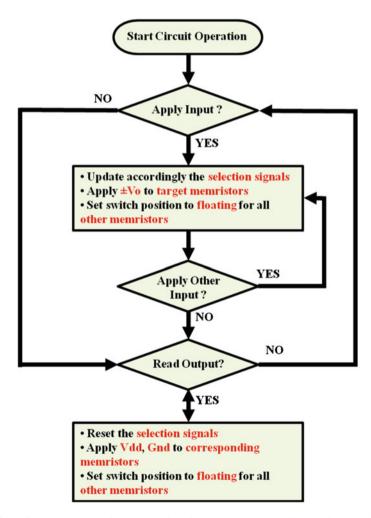

Chapter 4 addresses memristive logic design and computational methodologies. It includes a comprehensive summary of the most recognized memristive Boolean logic design concepts, which are based on collective memristive dynamics, and presents two novel circuit design methodologies based on memristors. Particularly, a new CMOS-*like* memristor-based circuit design approach and methodology that enables the creation of complementary logic, mapped onto a hybrid memristor/CMOS crossbar-based platform, is described. The proposed methodology is applied to the design and simulation of large combinational logic circuits, i.e. encoders and decoders. A proper, high-level design and simulation software tool for CMOS-*like* memristive logic circuits, which incorporates the developed memristor device model of Chap. 2, is also presented. The focus is then on the evolution of the memristor-based logic circuit design strategies from the proposed sequential stateful logic up to novel design schemes which support parallel processing of input signals.

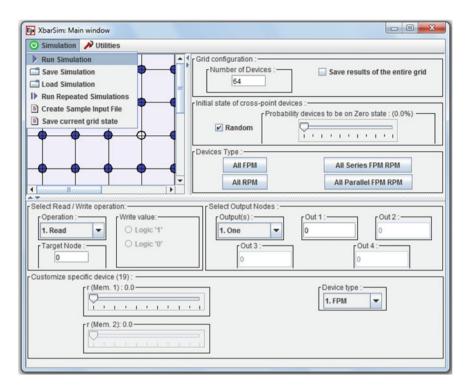

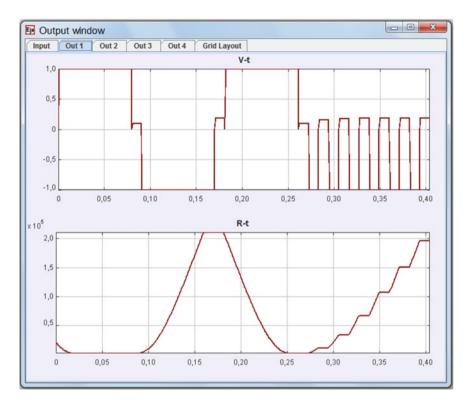

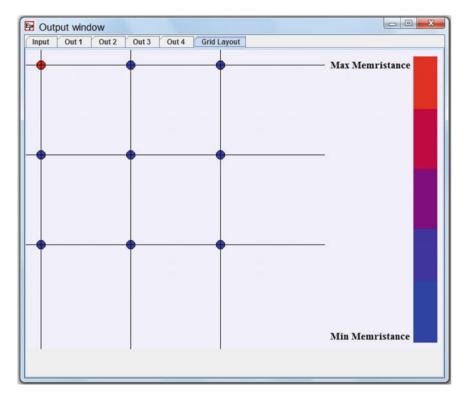

In Chap. 5 alternative crossbar architectures are introduced in an attempt to minimize the impact of the current sneak paths, while enabling larger array size and better read voltage margins towards more reliable memristor-based crossbar memories, compared to other approaches found in the literature. Moreover, novel memristive memory cell structures, comprising parallel/serial memristors, are investigated to possibly address the parasitic conducting problem. XbarSim, a high-level, educational GUI-based simulation environment which incorporates the proposed device model for memristive crossbar architectures, targeting memory or logic applications, is also presented.

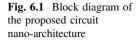

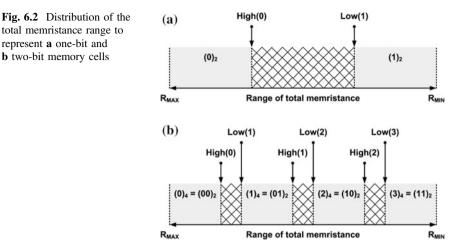

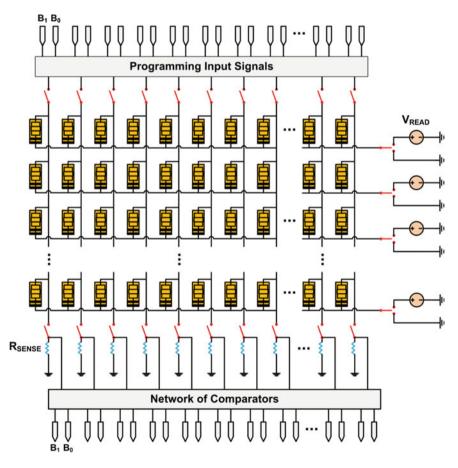

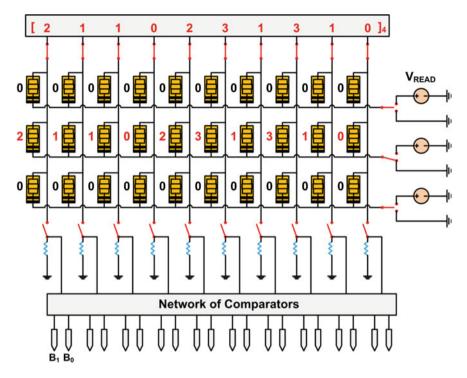

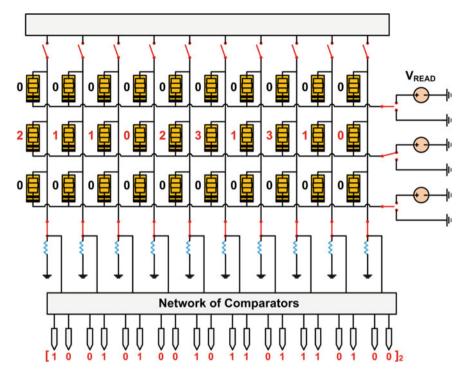

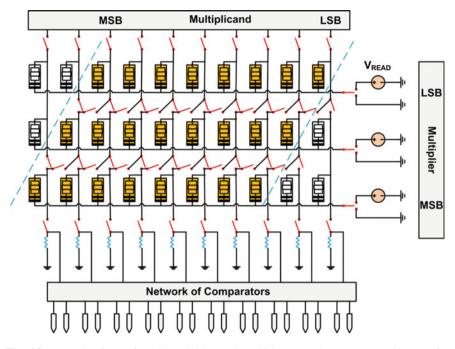

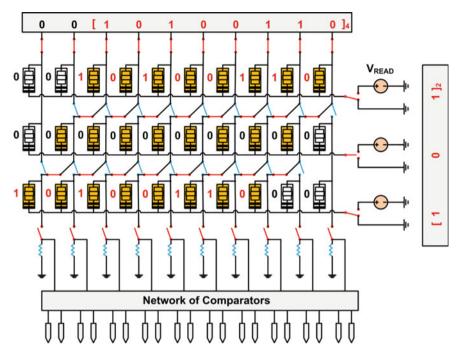

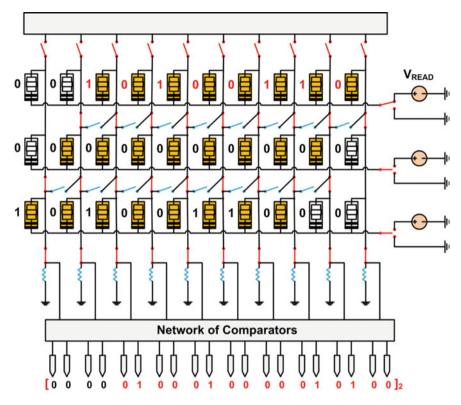

Chapter 6 presents an early approach to the design of a reconfigurable, memristor-based, arithmetic-logic unit (ALU) for future computing systems. The proposed ALU system combines CMOS peripheral circuitry with a high-density memristive multi-level crossbar, which allows the compact high-radix storage of numbers. The high-radix stored information is selectively converted to binary representation with the use of a network of comparators before it is supplied to a computational layer of fast adders. The memory module of the system allows for parallel read/write operations and achieves inherently the parallel creation of partial products, to be used for faster multiplication.

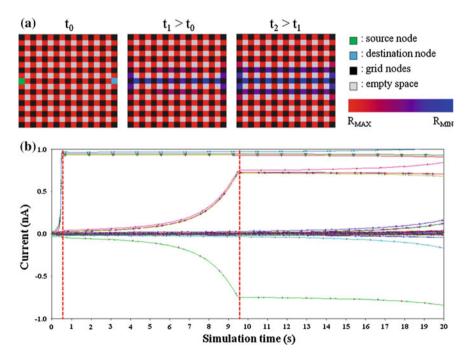

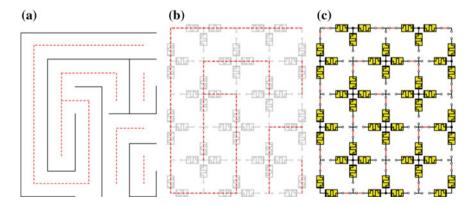

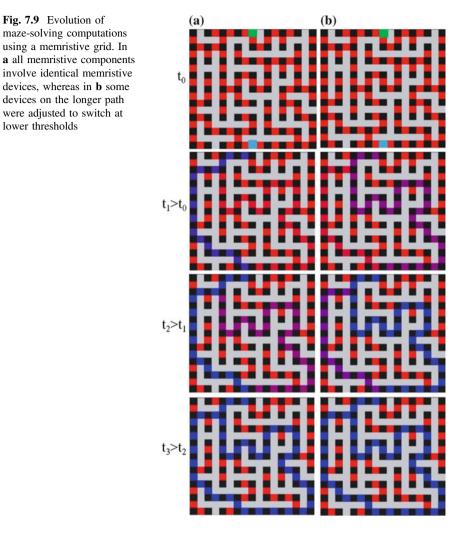

Chapter 7 explores memristive networks (grids) where emergent computation arises through collective device interactions. Computing efficiency of the grids is studied in several scenarios and new composite memristive structures are utilized in shortest path and maze-solving computations, addressing known problems of relevant published works in the recent literature. Some already published approaches are substantially extended by introducing modifications in the computing platform, thus leading to better results. Additionally, a methodology for the appropriate mapping of oriented graphs onto memristive networks, based on circuit models which correspond to several types of connections between graph vertices, is presented for the first time. This methodology simplifies the precise network projection of any mesh-based oriented graph via a one-to-one correspondence.

Preface

Chapter 8 concludes this Book providing a novel circuit-level Cellular Automata (CA)-inspired methodology for computational schemes capable of executing computations within memory. The novel computing structures are based on the threshold-based resistance switching behavior of multi-state composite memristive components located in array-like circuit structures. The unique composite circuit properties of memristors are exploited within CA-inspired circuit implementations, which are applied to solve several NP-hard problems of various areas of artificial intelligence.

Xanthi, Greece March 2015 Ioannis Vourkas Georgios Ch. Sirakoulis

# References

- International Technology Roadmap for Semiconductors (ITRS) (2013). Available: http:// www.itrs.net/. Accessed June 2014

- L.O. Chua, Memristor—the missing circuit element. IEEE Trans. Circuit Theory 18(5), 507–519 (1971)

- T. Prodromakis, C. Toumazou and L.O. Chua, Two centuries of memristors. Nature Materials 11(6), 477–557 (2012)

- D.B. Strukov, G.S. Snider, D.R. Stewart, R.S. Williams, The missing memristor found. Nature 453(May), 80–83 (2008)

- Y.V. Pershin, M. Di Ventra, Memory effects in complex materials and nanoscale systems. Adv. Phys. 60(2), 145–227 (2011)

- 6. L.O. Chua, If it's pinched it's a memristor. Semicond. Sci. Technol. 29(10), 104001 (2014)

- E. Linn, R. Rosezin, S. Tappertzhofen, U. Bottger, R. Waser, Beyond von Neumann-logic operations in passive crossbar arrays alongside memory operations. Nanotechnology 23(305205) (2012)

- Y.V. Pershin, M. Di Ventra, Neuromorphic, digital and quantum computation with memory circuit elements. Proc. IEEE 100(6), 2071–2080 (2012)

- Panasonic, The new microcontrollers with on-chip non-volatile memory ReRAM (2012). Available: http://panasonic.co.jp/corp/news/official.data/data.dir/jn120515-1/jn120515-1.html. Accessed 20 September 2014

- HP Cloud Source Blog, The Machine, a view of the future of computing (2014). Available: http://h30507.www3.hp.com/t5/Cloud-Source-Blog/The-Machine-a-view-of-the-future-ofcomputing/ba-p/164568#.VB2Bw5qKDGg. Accessed 20 September 2014.

- 11. R.P. Brent, P. Zimmermann, *Modern Computer Arithmetic* (Cambridge University Press, Cambridge, 2010)

المنسارات فكالاستشارات

# Contents

| 1 | Mer  | nristor Fundamentals                                   | 1  |

|---|------|--------------------------------------------------------|----|

|   | 1.1  | Introduction                                           | 1  |

|   | 1.2  | Memristor Defined by a State-Dependent Ohm's Law       | 2  |

|   | 1.3  | Fingerprints of Memristors                             | 3  |

|   | 1.4  | Memristor Defined by a "Pinched" Hysteresis Loop       | 4  |

|   | 1.5  | The "Ideal" Memristor                                  | 6  |

|   | Refe | erences                                                | 7  |

| 2 | Mer  | nristor Modeling                                       | 9  |

|   | 2.1  | Introduction                                           | 9  |

|   | 2.2  | A Novel Threshold-Type Memristor Circuit Model         | 10 |

|   | 2.3  | Modeling Memristors in SPICE                           | 15 |

|   | 2.4  | Model Verification                                     | 20 |

|   |      | 2.4.1 Fitting to a Reference Model                     | 20 |

|   |      | 2.4.2 Testing in Complex Memristive Circuits           | 23 |

|   | 2.5  | Overview and Comparison                                | 25 |

|   | Refe | erences                                                | 26 |

| 3 | Dyn  | amic Response of Multiple Interconnected Memristors    | 29 |

|   | 3.1  | Introduction                                           | 29 |

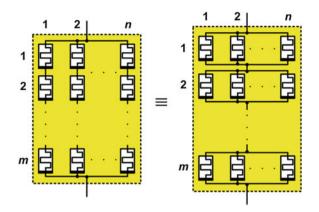

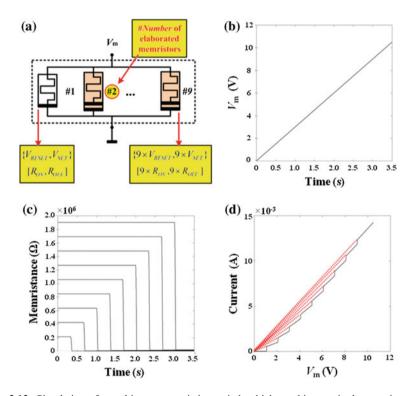

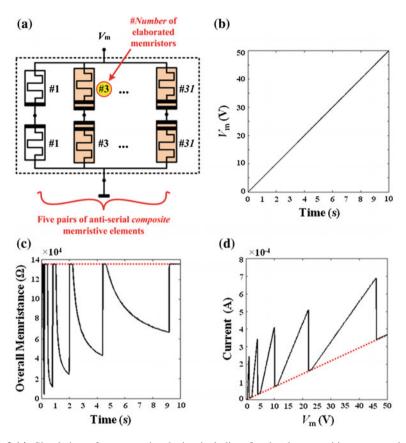

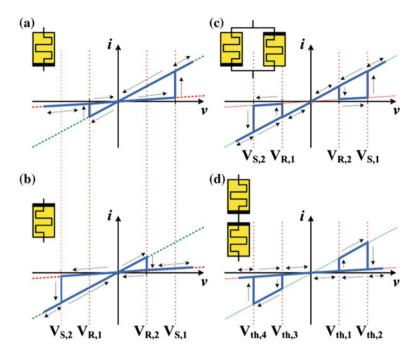

|   | 3.2  | Study of Composite Memristive Structures               | 31 |

|   |      | 3.2.1 Memristors Connected in Series                   | 31 |

|   |      | 3.2.2 Memristors Connected in Parallel                 | 41 |

|   | 3.3  | Generalized Concept for the Construction of Composite  |    |

|   |      | Memristive Systems                                     | 47 |

|   |      | 3.3.1 Circuit Examples Combining First/Second-Level    |    |

|   |      | Memristive Compositions                                | 49 |

|   |      | 3.3.2 Fine-Resolution Programmable Memristive Switches | 53 |

|   |      |                                                        |    |

المنسارات المستشارات

|   | 3.4  | Application of Composite Memristive Systems in Computing   |    |

|---|------|------------------------------------------------------------|----|

|   |      |                                                            | 55 |

|   | 3.5  |                                                            | 57 |

|   | Refe | rences                                                     | 58 |

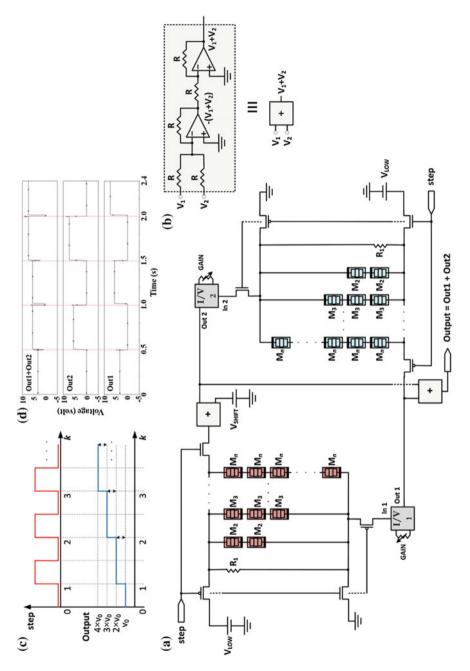

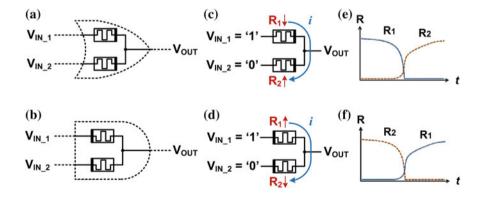

| 4 | Mer  | 0                                                          | 61 |

|   | 4.1  |                                                            | 61 |

|   | 4.2  | Switching Dynamics of Threshold-Type Memristors            |    |

|   |      | 1                                                          | 62 |

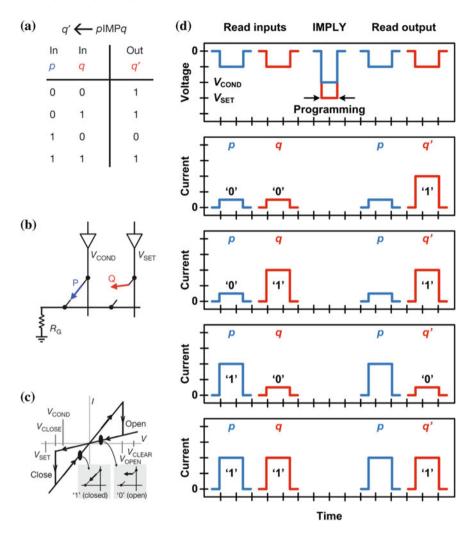

|   | 4.3  |                                                            | 64 |

|   |      | 1 7 6                                                      | 64 |

|   |      | 8                                                          | 67 |

|   |      | e                                                          | 69 |

|   | 4.4  |                                                            | 71 |

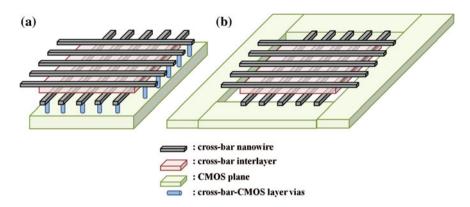

|   |      | 4.4.1 Implementation in Hybrid Nano-CMOS                   |    |

|   |      |                                                            | 74 |

|   |      |                                                            | 78 |

|   |      |                                                            | 82 |

|   |      | 1                                                          | 91 |

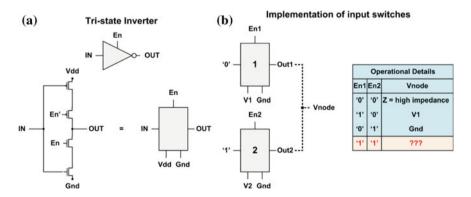

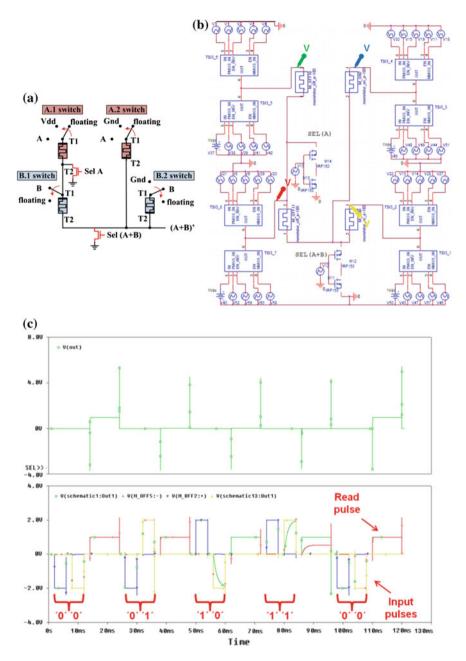

|   | 4.5  | A Memristive Logic Family for Parallel Processing          |    |

|   |      |                                                            | 92 |

|   |      | 4.5.1 Boolean Logic Operations Based on Threshold-Type     |    |

|   |      |                                                            | 93 |

|   |      |                                                            | 96 |

|   |      | 4.5.3 Overview and Comparison                              | 97 |

|   | Refe | rences                                                     | 98 |

| 5 | Mer  | ristive Crossbar-Based Nonvolatile Memory 1                | 01 |

|   | 5.1  |                                                            | 01 |

|   | 5.2  | Overview of Redox-Based RAM Device Technology 1            | 04 |

|   |      | 5.2.1 Metal Oxide-Bipolar Filamentary ReRAM 1              | 05 |

|   |      | 5.2.2 Metal Oxide-Unipolar Filamentary ReRAM 1             | 06 |

|   |      | 1                                                          | 06 |

|   | 5.3  | Memristive Memory Cell Operation Principles 1              | 07 |

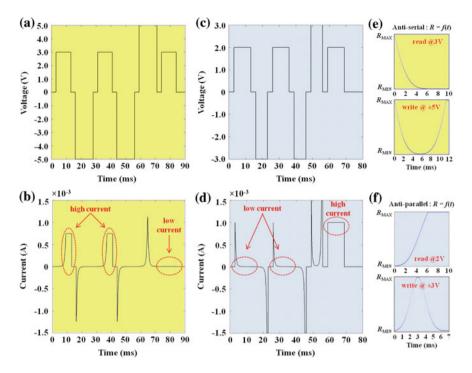

|   |      | 5.3.1 Anti-serial Memristive Switch (ASM) 1                | 09 |

|   |      | 5.3.2 Anti-parallel Memristive Switch (APM) 1              | 10 |

|   |      | 5.3.3 Pulse Properties of ASMs and APMs 1                  | 11 |

|   | 5.4  | Sneak-Path Challenge in Memristive Crossbar-Based Memory 1 | 13 |

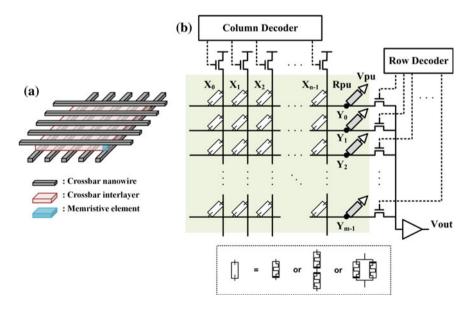

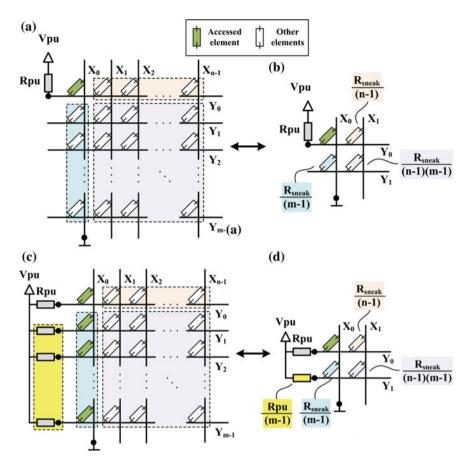

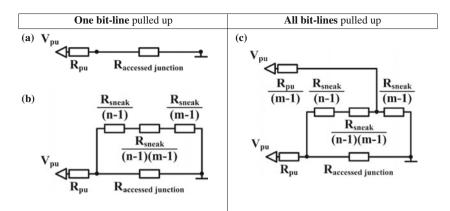

|   |      | 5.4.1 Fundamentals of Memristive Crossbar Based Memory 1   | 13 |

|   |      | 5.4.2 Estimation of Read Margins 1                         | 14 |

|   |      | •                                                          | 17 |

|   |      |                                                            | 19 |

|   |      | 5.4.5 Alternative Crossbar Topologies 1                    | 25 |

المتسارات

|   |              | 5.4.6 Simulation-Based Evaluation of Alternative         |     |

|---|--------------|----------------------------------------------------------|-----|

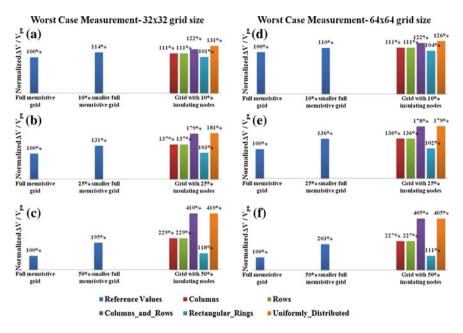

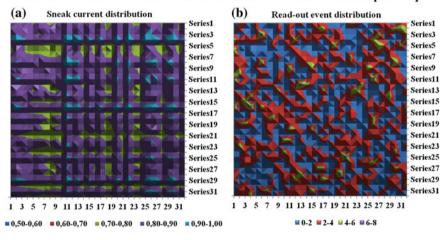

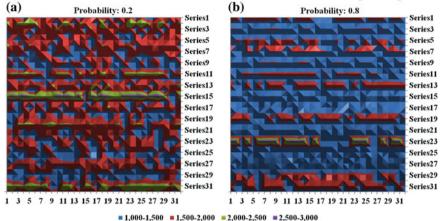

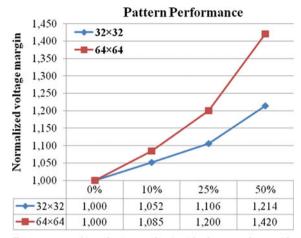

|   |              | Topologies                                               | 126 |

|   |              | 5.4.7 Application of Alternative Topologies to ASM-Based |     |

|   |              | Crossbar                                                 | 132 |

|   |              | 5.4.8 Overview and Discussion                            | 133 |

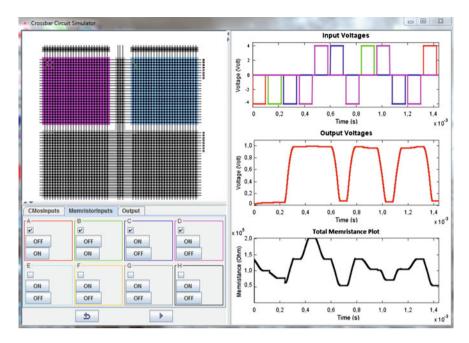

|   | 5.5          | XbarSim—An Educational Simulation Tool for Memristive    |     |

|   |              | Crossbar-Based Circuits                                  | 135 |

|   |              | 5.5.1 Details on the Simulated Circuit Topology          | 137 |

|   |              | 5.5.2 GUI-Based Simulation Procedure.                    | 140 |

|   |              | 5.5.3 Simulation Details—Crossbar Network Nodal          |     |

|   |              | Analysis                                                 | 141 |

|   | Refe         | erences                                                  | 144 |

|   |              |                                                          |     |

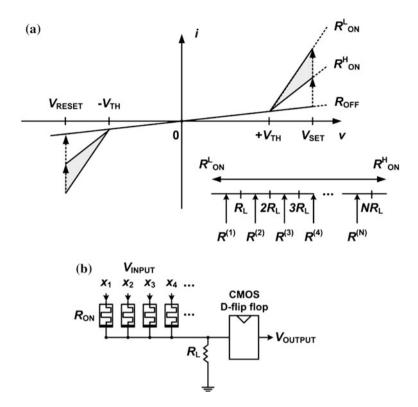

| 6 | Hig          | h-Radix Arithmetic-Logic Unit (ALU) Based on Memristors  | 149 |

|   | 6.1          | Introduction                                             | 149 |

|   | 6.2          | Overall Layout of the Memristive Multi-level             |     |

|   |              | Memory System                                            | 151 |

|   |              | 6.2.1 Multi-level Storage Cell                           | 152 |

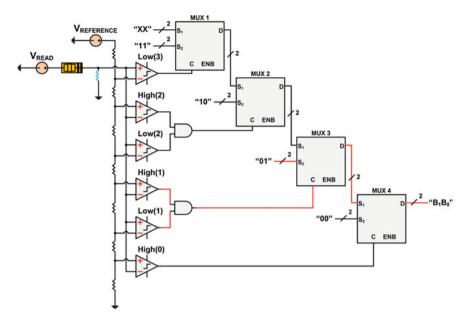

|   |              | 6.2.2 Analysis of the Circuit Topology                   | 155 |

|   | 6.3          | Enhanced Crossbar for Memristive ALU                     |     |

|   |              | with Built-in Memory                                     | 160 |

|   |              | 6.3.1 Parallel Creation of Partial Products for Fast     |     |

|   |              | Multiplication                                           | 162 |

|   | 6.4          | Simulation Results                                       | 164 |

|   | 6.5          | Overview and Discussion                                  | 169 |

|   | Refe         | erences                                                  | 170 |

| - | <b>N</b> T 4 |                                                          | 170 |

| 7 |              | works of Memristors and Memristive Components            | 173 |

|   | 7.1          | Introduction                                             | 173 |

|   | 7.2          | Memristive Network-Based Computations.                   | 175 |

|   |              | 7.2.1 Description of the Computing Platform              |     |

|   |              | and Its Function                                         | 176 |

|   |              | 7.2.2 Memristive Circuits for Modeling Edges of Directed |     |

|   |              | (Oriented) Graphs                                        | 179 |

|   | 7.3          | Path Computing and Maze-Solving with Ariadne's           |     |

|   |              | Memristive Thread                                        | 181 |

|   |              | 7.3.1 Fully Interconnected Network                       | 181 |

|   |              | 7.3.2 Defective Network                                  | 185 |

|   |              | 7.3.3 Maze-Solving                                       | 187 |

|   | 7.4          | Mapping Problems Defined in Directed Graphs              | 192 |

|   | 7.5          | Overview and Discussion                                  | 194 |

|   | Refe         | erences                                                  | 196 |

المتسارات

| 8 | Men  | nristive Computing for NP-Hard AI Problems             | 199 |

|---|------|--------------------------------------------------------|-----|

|   | 8.1  | Introduction                                           | 199 |

|   | 8.2  | Basics of Cellular Automata and Suitable HW Structures |     |

|   |      | for Their Implementation                               | 200 |

|   | 8.3  | Application Mapping Methodology to Memristive          |     |

|   |      | CA-Based Circuits                                      | 203 |

|   | 8.4  | Solving NP-Hard Artificial Intelligence Problems       | 206 |

|   |      | 8.4.1 Shortest Path and Traveling Salesman Problems    | 206 |

|   |      | 8.4.2 The Max Clique Problem                           | 213 |

|   |      | 8.4.3 The Sorting Problem                              | 217 |

|   |      | 8.4.4 The Bin Packing Problem.                         | 222 |

|   |      | 8.4.5 The Knapsack Problem                             | 231 |

|   | 8.5  | Overview and Comparison                                | 237 |

|   | Refe | rences                                                 | 239 |

المتسارات

# Abstract

In the last decades, exponential reduction of integrated circuits feature size and increase in operating frequency was achieved in Very Large Scale Integration (VLSI) fabrication industry using conventional Complementary Metal-Oxide-Semiconductor (CMOS) technology. However, dimensional scaling of CMOS is expected to soon reach fundamental physical limits and this has driven great research efforts in emerging nanoelectronic devices over the last decade. Several new alternative information processing devices and architectures for existing or new functions, are being explored in an attempt to sustain the historical integrated circuit performance increase. To this end, the semiconductor industry today is facing two main challenges related to extending integrated circuit technology to beyond the limits of CMOS scaling: (i) to propel CMOS beyond its ultimate functionality by integrating a new high-performance memory technology onto the CMOS platform; (ii) to extend information processing far beyond that achievable by CMOS, using new devices which will either complement CMOS components or will eventually replace them completely. Among many nanotechnologies currently under intense investigation, resistance-switching devices generally referred to as "memristors" show great potential and the focused R&D efforts in many industrial laboratories make this technology widely considered as a potential successor of CMOS-based storage and processing cells in future electronic systems.

Memristor (concatenation of "memory resistor"), is the 4th fundamental circuit element, predicted by Chua in 1971 (joining the resistor, the capacitor, and the inductor), which represents one of today's latest technological achievements. Memristor (here used to refer both to an "ideal" memristor as well as to a generalized memristive system) is a passive two-terminal electronic device whose behavior is described by a nonlinear constitutive relation between the voltage drop at its terminals and the current flowing through the device. The reason why memristors are substantially different from the other fundamental circuit elements is that, when the applied voltage is turned off, they still remember how much voltage was applied before and for how long; thus presenting memory of their past. However, this innovative device attracted most of attention worldwide only after 2008 when the first practical implementation was announced by Hewlett-Packard

(HP) Laboratories, originating intense research activity ever since. The increasing interest and the active involvement of industry-leading companies in future production of memristor-related products and pioneering memristive architectures, as well as the continuous improvement of the memristance-switching behavior thanks to the incessant accumulation of knowledge about the underlying device materials, are encouraging for the future implementation and establishment of memristive circuits and systems.

This book considers the design and development of nanoelectronic circuits and architectures focusing particularly on memristors. The ultimate goal is to study, explore, and address the related challenges and propose solutions for the smooth transition from conventional circuit technologies to emerging nanotechnologies. To this end, several new results on memristor modeling, memristive interconnections, logic circuit design, memory circuit architectures, computer arithmetic systems, development of design and simulation software tools, and applications of memristors in computing, are presented. Memristor device modeling constitutes a necessary first step towards further investigation and experimentation. After a brief introduction to the fundamentals of memristors in Chap. 1, memristor modeling is the focus of Chap. 2 where a threshold-type model of a voltage-controlled bipolar memristor is presented. Threshold-type switching is closer to the actual behavior of most experimentally realizable devices and the developed model attributes the resistance-switching behavior to a tunneling-distance modulation. Throughout the rest of the book, which spans a wide range of memristor-related topics and gives a nice overview of the current research trends, all analyses and simulations are based on this model. Specifically, complex memristive interconnections are studied in Chap. 3 in an attempt to explain and harness the threshold-dependent sophisticated composite behavior of multiple interconnected devices. The exploitation of the threshold-type switching of memristors and memristive compositions enabled the design of digital logic circuits as presented in Chap. 4. A CMOS-like memristor-based logic family that enables the creation of complementary logic in the crossbar geometry, is introduced. Memristors, which here are used as two-state switches rather than analog devices, serve both for information encoding and computation. This chapter also presents a software tool which allows the design and simulation of memristive CMOS-like circuits via a user-friendly graphical user interface (GUI). The chapter closes with the presentation of a logic design strategy which enables parallel processing of input signals, delivering high-performance resistive logic circuits. Crossbar-based resistive random access memory (ReRAM), a powerful promising alternative to existing baseline memory technologies, is the focus of Chap. 5. Mathematical analyses and simulation results of innovative approaches to memory cell structure and memory architecture, which alleviate the impact of the unwanted sneak currents by improving the read-out sense voltage-margins, are presented. The chapter closes with the demonstration of XbarSim, an educational simulation environment which was developed for the study of crossbar-based memristive circuits and which was used in all relevant conducted simulations whose results appear in this chapter. In Chap. 6 we exploit the multi-bit storage capability and the small footprint of memristors to propose a

novel CMOS-compatible high-radix arithmetic-logic unit (ALU) for future computing systems. The proposed ALU combines CMOS peripheral circuitry with a high-density memristive crossbar which comprises multi-state composite memristive switches and allows the compact high-radix storage of numbers. Chapter 7 presents system-level applications of memristors and composite memristive structures. Memristors create a new opportunity for realization of innovative circuits that are not possible or have inefficient realization in the present circuit design domain. So, this chapter explores memristive networks where emergent computation arises through collective device interactions, something promising to revolutionize hardware computing architectures. Computing efficiency of the networks is studied in several scenarios and composite memristive components are utilized for the solution of known, inherently complex in terms of computation time, problems in a massively parallel way. Finally, Chapter 8 presents a novel circuit-level Cellular Automata (CA)-inspired methodology for computational schemes capable of executing computations within memory. CA constitute a well-studied, inherently parallel, computing paradigm able to capture globally emerging behavior from the collective interaction of simple and local components. The proposed computing structures exploit the threshold-based resistance switching behavior of memristors and of their multi-state composite components in array-like circuit structures where the sparse nature of computations resembles certain operational features of CA. This way, a powerful computational tool is combined with the unique circuit properties of memristors within CA-inspired implementations which are applied to efficiently solve NP-hard artificial intelligence (AI) problems.

# Chapter 1 Memristor Fundamentals

The *memristor* is considered one of the most promising nano-devices among those currently being studied for possible use in electronic systems of the future. The best performance features which have been demonstrated in published experimental results regarding research device prototypes so far include fast switching speed, high endurance and data retention, low power consumption, high integration density, and (perhaps most importantly) CMOS compatibility. Undoubtedly, the combination of such advantageous characteristics in a single device justifies the phenomenal research interest that resistance-switching devices have generally attracted over the last few years and verify the existing rumors about their potential application in both storage and processing units of future electronic systems. Memristive nano-devices are the focus of this book and this chapter aims to introduce the reader to their fundamental properties on which the presented study is based.

# 1.1 Introduction

The concept of the "ideal" *memristor* (concatenation of "memory resistor") was first introduced in 1971 [1] as a two-terminal circuit element that linked the remaining missing pair of the four basic circuit variables, namely, *flux* and *charge*, as shown in Fig. 1.1. It was thus formally defined as the fourth fundamental circuit component (joining the resistor, the capacitor, and the inductor). A few years later, Chua and Kang [2] introduced to the scientific community the generic properties of a broad generalization of the memristor to an interesting class of nonlinear dynamical devices, called memristive devices. This chapter presents a summary of the memristor from a circuit-theoretic perspective, independent of the material the device is made of, and focuses on the information necessary to capture the memristor fundamentals and move on with the more-technical content of the chapters that follow.

© Springer International Publishing Switzerland 2016

I. Vourkas and G.Ch. Sirakoulis, *Memristor-Based Nanoelectronic Computing Circuits and Architectures*, Emergence, Complexity and Computation 19, DOI 10.1007/978-3-319-22647-7\_1

# 1.2 Memristor Defined by a State-Dependent Ohm's Law

Normally there are two mathematical representations of time-invariant memristors depending on whether the input signal is a current source (current-controlled memristor) or a voltage source (voltage-controlled memristor). In a broader sense, any two-terminal electrical device is called a memristor if its behavior is described by a nonlinear constitutive relation between the voltage drop at its terminals v and the current flowing through the device i, as shown below:

Current-controlled memristor:

$$\nu = R(x)i \tag{1.1}$$

with the state equations:

$$\frac{\mathrm{d}x}{\mathrm{d}t} = f(x, i) \tag{1.2}$$

Voltage-controlled memristor:

$$i = G(x)v \tag{1.3}$$

with the state equations:

$$\frac{\mathrm{d}x}{\mathrm{d}t} = g(x, v) \tag{1.4}$$

The scalars R(x) and G(x) are called memristance and memductance (acronyms for memory resistance/conductance), respectively, and have units Ohm ( $\Omega$ ) and Siemens (S). The state-vector  $x = (x_1, x_2, ..., x_n)$  has  $n \ge 1$  components  $x_1, x_2, ..., x_n$

called state-variables, which represent internal physical parameters and do not depend on any external variables, such as voltages or currents.

#### **1.3** Fingerprints of Memristors

Memristors have a unique set of "fingerprints", i.e. two important common properties which distinguish them among other resistance-switching electronic devices. The first is the "pinched" current–voltage (i-v) hysteresis loop which must hold for all amplitudes, for all frequencies, and for all initial conditions of any periodic waveform which assumes both positive and negative values over each period. In other words, there is no time delay (i.e. no phase-shift) between the voltage and the current waveforms since v(t) = 0 whenever i(t) = 0 for current-controlled memristors, or i(t) = 0 whenever v(t) = 0 for voltage-controlled memristors. The nonvolatile memory property of memristors is a direct consequence of the state-dependent Ohm's Law in Eqs. 1.1 and 1.3. It is important to note that, if one opens or short-circuits a memristor having a resistance  $R_0$  at  $t = t_0$  so that v = 0and i = 0, the memristor does not lose its state information but it instead holds its state unchanged (ideally) forever!

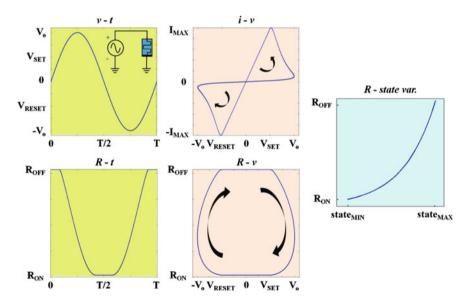

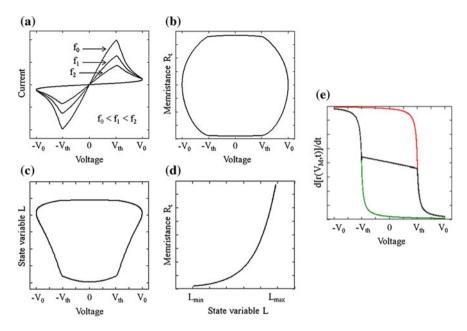

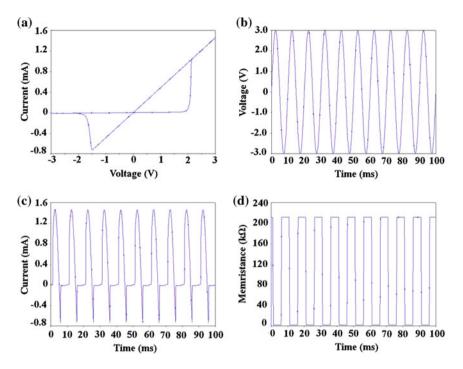

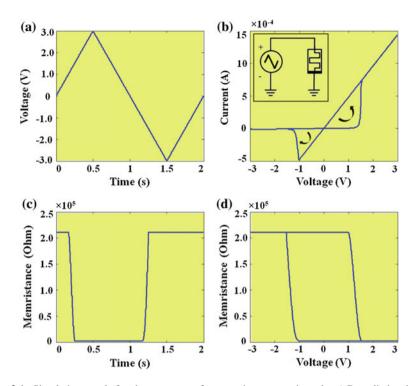

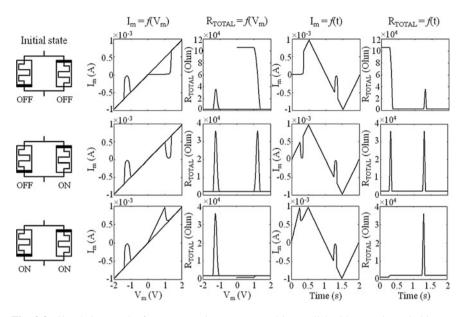

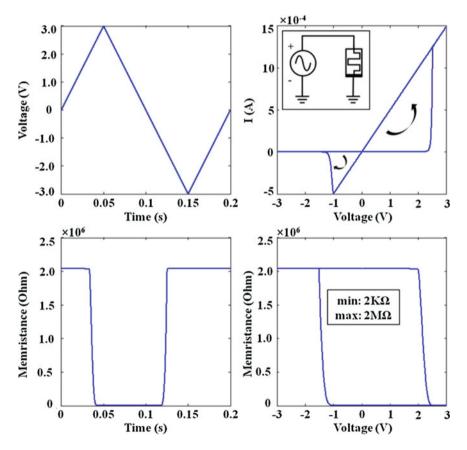

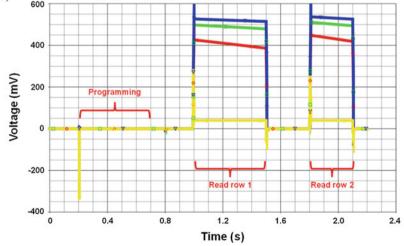

This property is seen in Fig. 1.2 which shows qualitatively the response of a voltage-controlled, threshold-type switching bipolar memristor to a sinusoidal AC

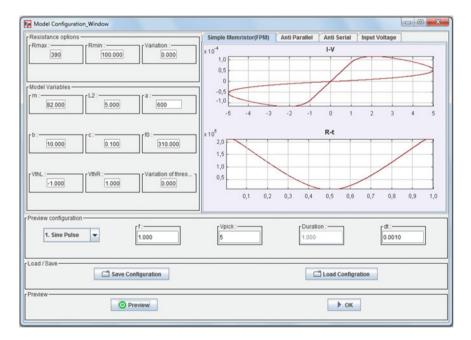

**Fig. 1.2** Qualitative representation of the response of a voltage-controlled, threshold-type switching bipolar memristor to a sinusoidal AC applied voltage according to the model presented in Chap. 2. The simulation graphs include the applied voltage (v-t), the hysteretic current–voltage (i-v) characteristic, the change of the memristance with time (R-t) and with the applied voltage (R-v), respectively, as well as the memristance-state map

applied voltage. Threshold-type switching is closer to the actual behavior of most experimentally realizable memristive devices [3]; the resistance switching rate is small below (fast above) a voltage threshold (namely  $V_{\text{SET}}$  or  $V_{\text{RESET}}$ ) which is viewed as the minimum voltage required to induce a change to the memristance of the device. The graphs shown in Fig. 1.2 include the applied voltage signal (*v*–*t*), the hysteretic current–voltage (*i*–*v*) characteristic, the corresponding change of the memristance with time (*R*–*t*) and with the applied voltage (*R*–*v*), respectively, as well as the memristance plotted as a function of the state-variable (memristance-state map).

The memristance-state map is a very useful graph because it shows how to navigate from one memristance  $R_0$  at state  $s_0$  to another memristance  $R_1$  at state  $s_1$  by applying a voltage pulse of properly selected amplitude and duration; it therefore allows one to tune the memristor's resistance continuously (in the chapters that follow we will refer to this analog operation of memristors which is still difficult to be achieved experimentally in a reliable manner). On the contrary, the rest of the plots shown in Fig. 1.2 cannot be used to predict the response given any other excitation waveform different from the depicted one. A "pinched" i-v is not unique but varies with the input waveforms, as well as the amplitude and the frequency. While a pinched i-v loop, measured from an experimental device, implies that a device is a memristor, it is completely useless by itself as a model as it cannot predict the response to an arbitrary input signal. The only way to do this is via the memristance-state map. The latter obeys the Ohm's Law, except that the memristance is not constant, as illustrated in Fig. 1.2, but it depends on a dynamical state-variable which evolves according to a prescribed state-equation as Eqs. 1.2 and 1.4.

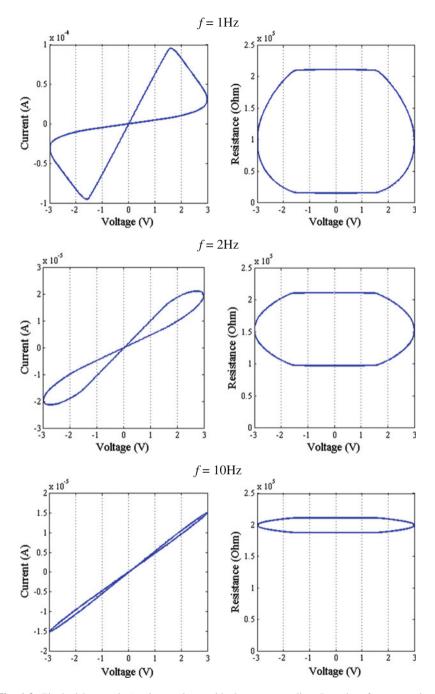

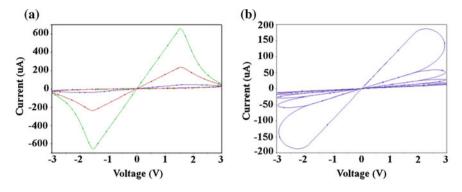

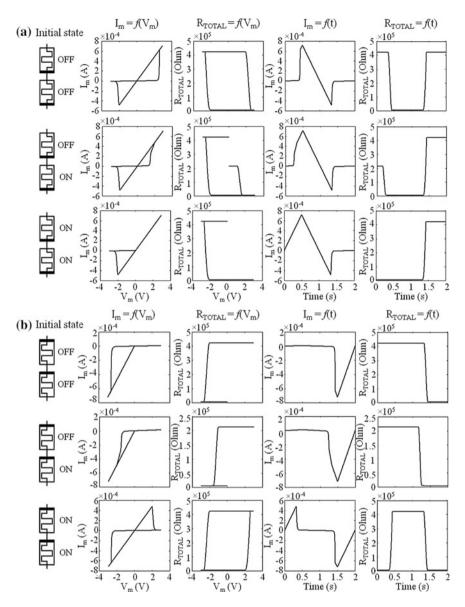

The other unique property shared by all memristors is that, as the frequency of the applied periodic signal increases, the area enclosed within each part of the *i*-v sub-loop in the first and third quadrants deforms and shrinks continuously. The graph tends to collapse to a straight line (a single-valued function) which passes through the origin. In other words, high-frequency input signals do not give the memristor the time required for it to change its state. This property is confirmed in Fig. 1.3 which shows three different  $\{i-v, R-v\}$  pairs of a voltage-controlled memristor under sinusoidal excitations of the same amplitude but of different frequencies. The memristor is initially found in the high resistive state whereas the minimum achieved resistance differs each time, thus causing a different i-v plot. The above criteria of *pinched hysteresis loop* and the *single-valued function limiting phenomenon* as  $\omega \rightarrow \infty$  must hold for all memristors.

# 1.4 Memristor Defined by a "Pinched" Hysteresis Loop

As Chua himself stressed in one of his most recent papers [4], for a device to be called a memristor, its hysteresis loop must be pinched and must pass through the origin in the i-v plane. A hysteresis loop is said to be pinched at the origin if it always passes through the origin at all time instants when the input signal waveform is zero. However, it is important to understand that pinched hysteresis loops are not

**Fig. 1.3** Pinched hysteretic i-v loops along with the corresponding R-v plots for a memristor under a sinusoidal applied voltage of the same amplitude but of different frequency *f* according to the model presented in Chap. 2

models because "models must predict" but pinched hysteresis loops cannot predict what happens if another waveform is applied across the device. Any two distinct periodic input signals would give distinct pinched hysteresis loops associated with a particular memristor, thus they constitute an "identity card" of that particular device.

Indeed, from an experimental perspective a memristor is best defined as any two-terminal device that exhibits a pinched hysteresis loop in the v-i plane when driven by any periodic voltage or current signal. This definition greatly broadens the scope of memristive devices to encompass even non-semiconductor devices, both organic and inorganic [5]. It is also in line with the original definition of the ideal memristor in [1], thus pinched hysteresis loops are in fact the hallmarks of all memristors, ideal or generic. Nevertheless, pinched hysteresis loops of ideal memristors must be odd symmetric, thus any non-volatile resistive memory device that exhibits a pinched hysteresis loop that is not odd symmetric, such as those shown in the following chapters, must be modeled as a generic memristor.

# 1.5 The "Ideal" Memristor

Let us consider the "ideal" case where the state equations Eqs. 1.2 and 1.4 are f(x, i) = i and g(x, v) = v, respectively. Therefore, integrating both sides of these equations respectively gives:

$$x(t) = \int_{-\infty}^{t} i(\tau) d\tau = q(t)$$

(1.5)

$$x(t) = \int_{-\infty}^{t} v(\tau) d\tau = \varphi(t)$$

(1.6)

Now substituting Eqs. 1.5 and 1.6 for x in Eqs. 1.1 and 1.3 respectively, and integrating both sides, gives:

$$\varphi(t) = \int_{-\infty}^{t} v(\tau) d\tau = \int_{-\infty}^{t} R(q(\tau)) \frac{dq(\tau)}{d\tau} d\tau = \int_{q(-\infty)}^{q(t)} R(q) dq = \hat{\varphi}(q(t)) \quad (1.7)$$

$$q(t) = \int_{-\infty}^{t} i(\tau) d\tau = \int_{-\infty}^{t} G(\varphi(\tau)) \frac{d\varphi(\tau)}{d\tau} d\tau = \int_{\varphi(-\infty)}^{\varphi(t)} G(\varphi) d\varphi = \hat{q}(\varphi(t)) \quad (1.8)$$

#### 1.5 The "Ideal" Memristor

The above equations indicate that in this degenerate special scalar case, the two equations Eqs. 1.1 and 1.2 (resp. Eqs. 1.3 and 1.4) defining a current-controlled (resp. a voltage-controlled) memristor are equivalent to a single equation:

$$\varphi = \hat{\varphi}(q) \tag{1.9}$$

for a charge-controlled memristor, or

$$q = \hat{q}(\phi) \tag{1.10}$$

for a *flux*-controlled memristor.

The latter are precisely the fourth constitutive relationship shown in Fig. 1.1, defining the memristor via an axiomatic approach where the variables q and  $\varphi$  do not need to have precise physical significance. Differentiating Eqs. 1.9 and 1.10 with respect to time t, we obtain:

$$v = \frac{\mathrm{d}\varphi}{\mathrm{d}t} = \frac{\mathrm{d}\hat{\varphi}(q)}{\mathrm{d}q}\frac{\mathrm{d}q}{\mathrm{d}t} = R(q)i \tag{1.11}$$

and

$$i = \frac{\mathrm{d}q}{\mathrm{d}t} = \frac{\mathrm{d}\hat{q}(\varphi)}{\mathrm{d}\varphi} \frac{\mathrm{d}\varphi}{\mathrm{d}t} = G(\varphi)v \tag{1.12}$$

It follows from Eq. 1.11 that the charge-controlled memristor defined in Eq. 1.9 is equivalent to a charge-dependent Ohm's Law where R(q) is just the slope of the curve  $\varphi = \varphi(q)$  at q. Of course, Eqs. 1.9 and 1.11 are equivalent and one can recover Eq. 1.9 by integrating both sides of Eq. 1.11 with respect to t.

Since experimental devices obeying the ideal constitutive relation of Eq. 1.9 or Eq. 1.10 are rather rare, most memristor prototypes will be rather modeled as generic memristive devices according to Eqs. 1.1–1.2 or Eqs. 1.3–1.4. Such model of a generic memristive device is presented in Chap. 2 and is later used in the rest of this Book. However, for terminology reasons, we will henceforth refer to all such devices as memristors and call only the fourth circuit element of Fig. 1.1 as an "ideal" memristor whenever a distinction is required.

The chapters that follow span a wide range of memristor-related topics and give a good overview of the ongoing research and the current trends in this exciting scientific field.

#### References

- 1. L.O. Chua, Memristor—the missing circuit element. IEEE Trans. Circuit Theory 18(5), 507–519 (1971)

- 2. L.O. Chua, S.M. Kang, Memristive devices and systems. Proc. IEEE 64(2), 209-223 (1976)

- 3. Y.V. Pershin, M. Di Ventra, Memory effects in complex materials and nanoscale systems. Adv. Phys. **60**(2), 145–227 (2011)

- 4. L.O. Chua, Resistance switching memories are memristors. Appl. Phys. A Mater. Sci. Process. **102**(4), 765–783 (2011)

- 5. V. Erokhin, Organic memristors: basic principles, in *IEEE International Symposium on Circuits and Systems (ISCAS)*, Paris, France (2010)

# Chapter 2 Memristor Modeling

# 2.1 Introduction

Since the exciting discovery of nonvolatile memristive behavior in Titanium dioxide (TiO<sub>2</sub>)-based nano-films at Hewlett Packard (HP) Labs in 2008 [1], both academia and industry have been engaged in the search for novel memristive materials and manufacturing technologies. HP's version of the TiO<sub>2</sub> substrate memristor remains up to now the most generally recognized memristor type. It is based on two thin-layer TiO<sub>2</sub> films. The bottom layer acts as an insulator whereas the top film layer acts as a conductor via oxygen vacancies in the TiO<sub>2</sub>; TiO<sub>2</sub> changes its resistance in the presence of oxygen. Voltage increment moves the oxygen vacancies from the top layer towards the bottom layer, thus changing its resistance. A great deal of ongoing work has been devoted to the development of mathematical models capable to capture the complex dynamics exhibited by these nanostructures. An appropriate descriptive model will not only lead to a better understanding of its behavior, but will also result to a better exploitation of its unique properties in novel systems and architectures combining data storage and data processing in the same physical location.

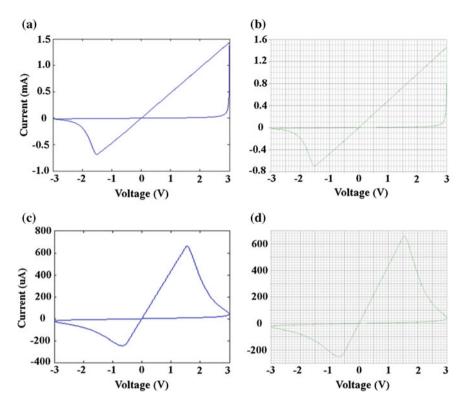

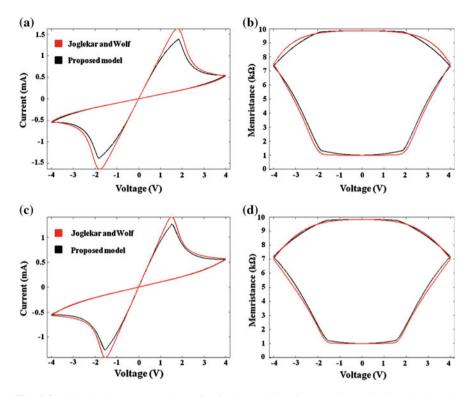

Currently there are several available device models which attempt to characterize both current–voltage (i–v) behavior as well as the device dynamics [2–9]. The HP group, in their first memristor implementation announcement, suggested a coupled variable-resistor model for memristors [1]. This model was later improved by Joklegar and Wolf [10], whereas several papers by HP [11, 12] reported on further developments of resistance switching theory for TiO<sub>2</sub>-based devices. Nevertheless, until nowadays there has been no direct connection between a model and the memristor physical properties. Only a few models were derived on the basis of material characterization and experimental electronic measurements, thus giving some hint on the physical mechanisms at the origin of the unique behavior of memristors [9, 13]. However, given the complexity of the physical processes that occur in the devices, the corresponding detailed mathematical descriptions are

I. Vourkas and G.Ch. Sirakoulis, *Memristor-Based Nanoelectronic Computing Circuits and Architectures*, Emergence, Complexity and Computation 19, DOI 10.1007/978-3-319-22647-7\_2

<sup>©</sup> Springer International Publishing Switzerland 2016

usually far too complex to solve analytically and numerical solutions are too time consuming to include in a simulation. Moreover, since simulation with Simulation Program with Integrated Circuit Emphasis (SPICE) is common practice in circuit development, several models of memristors were also implemented in SPICE [2, 5–8, 14–20].

The study of some of the most noteworthy published memristor models has shown that simple models are able to reproduce most of the dynamics observed with more accurate models, whose far greater computational complexity may lead to convergence problems and instability issues in complex circuits [21]. For example, the original linear oxygen vacancy drift model proposed by HP is valid only for certain choices of input signals and initial state of the memristance. Furthermore, a common problem in most models is that there is no threshold consideration. Threshold-type switching, though, is an extremely important common feature of the majority of experimental memristive devices. Physical memristor devices demonstrate a threshold voltage where hysteresis is not seen unless the voltage across the memristor exceeds the threshold [22]. Another important feature concerns the switching speed of memristors during the "set" and "reset" operations which generally are not similar [9, 22]. According to characterization data from HP Labs, the motion of the memristor state variable depends both on its current state and on the polarity of the applied voltage [9], something which could be attributed to the interaction of the external applied field, the internal field of the concentrated defects (e.g. charge traps, mobile ions, oxygen vacancies, etc.), and the diffusion, all acting in the same or in the opposite directions according to the applied voltage.

In the rest of this chapter we present a SPICE-compatible device model [23] of a voltage-controlled memristor which explains memristive behavior while primarily attributing the switching effect to an effective tunneling distance modulation [24]. This model aims to address most of the aforementioned shortcomings; it satisfies the desired memristive fingerprints [25] and involves significantly low-complexity operation under an unlimited set of frequencies over a wide range of applied voltages. The SPICE simulation results are found in good qualitative and quantitative agreement with the theoretical formulation of the model [26]. Also, the model represents well the complex switching behavior of memristor when fitted to other widely used published models. Therefore, it can be used to provide accurate enough circuit simulations for a wide range of memristor devices and voltage inputs, while it can be incorporated as a circuit element in any current computer-aided memristor-based circuit design work.

# 2.2 A Novel Threshold-Type Memristor Circuit Model

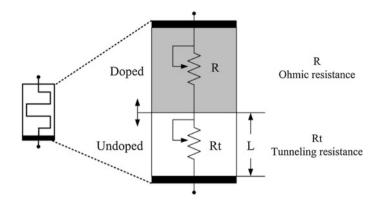

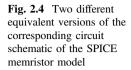

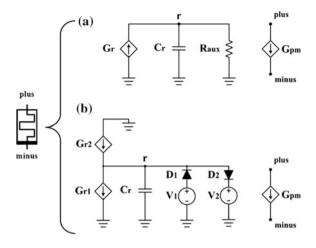

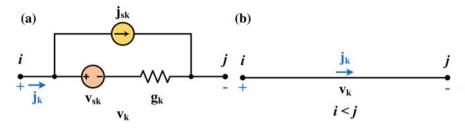

Inspired from the original circuit model proposed by HP for  $TiO_2$ -based devices, the equivalent circuit of the proposed memristor model is depicted in Fig. 2.1.

Fig. 2.1 Equivalent circuit of the coupled ohmic-tunneling variable-resistor circuit model

It concerns a threshold-type switching model of a two-terminal voltage-controlled electrical device that exhibits memristive behavior, whose general definition is given by the following equations:

$$I(t) = G(L, t)V_M(t)$$

(2.1)

$$\dot{L} = f(V_M, t). \tag{2.2}$$

Parameter *L* denotes the single state variable of the system (indicating the internal memristor state), which in our model is the tunnel barrier-width (e.g. the thickness of the free of oxygen vacancies dioxide layer), with the electrical current transport process being limited primarily by tunneling through it. *G* is the conductance (memductance) of the device, whereas *I* and  $V_M$  represent the flowing current and the applied voltage, respectively. In the coupled ohmic-tunneling variable-resistor equivalent circuit of Fig. 2.1, we consider an ohmic variable-resistor *R* and a tunneling variable-resistor *Rt* connected in series. *R* represents the resistance of the doped dioxide layer and *Rt* represents the tunneling resistance of the undoped layer of the device. The doped layer acts as a conductor whereas the undoped layer is a pure insulator. Therefore, there is a significant difference between the actual values of their resistances, with  $Rt \gg R$ , which is the reason why the model concentrates mainly on Rt.

The tunneling resistance Rt is expected to be proportional to the tunnel barrier width L, given the fact, that the larger the barrier width the higher the resulting resistance should be. Also, its value is anticipated to change according to the "movement" of the boundary between the two layers because of the transport of oxygen deficiencies under positive or negative applied voltage. Thus, any mathematical formulation for Rt could include at least a fitting parameter which would bound the effect of the varying geometry of the device on the actual concentration of the oxygen vacancies in either the doped or the undoped side of the film.

Furthermore, according to Schiff [24], Rt is inversely proportional to the product of the voltage-dependent tunneling transmission coefficient ( $T_0$ ) and the electron effective density of states ( $N_{eff}$ ), whereas it is exponentially proportional to the tunnel barrier-width (L). Therefore, its particular mathematical formulation is:

$$Rt(V_M) = \frac{1}{N_{eff}} \cdot \frac{e^{2k_{V_M}L}}{T_{0,V_M}}.$$

(2.3)

The voltage dependence of Eq. 2.3, due to the presence of the voltage-dependent parameters  $T_0$  and k, can be translated into a corresponding variation of L; it can be passed to a new voltage-dependent parameter  $L_{V,t}$  with no significant error implication. In this model we define Rt to be described by the following equation:

$$Rt(L_{V_M,t}) = f_0 \cdot \frac{e^{2L_{V_M,t}}}{L_{V_M,t}}.$$

(2.4)

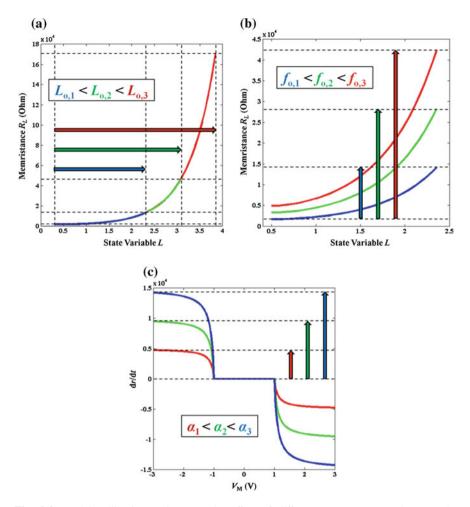

Equation 2.4 gives the resistance (memristance) of the device for a certain restricted range of the state variable *L*. All unknown material-specific and geometrical issues are contained into the model-fitting constant parameter  $f_0$ . The qualitative agreement of Eqs. 2.3 and 2.4 verifies our assumption for the exponential dependence of *Rt* on *L*. Moreover, Pickett et al. in [9] reported on experimental results from the application of a dynamical testing protocol applied to a set of TiO<sub>2</sub>-based memristive devices. Through analysis of the switching dynamics that arise from ionic motion in the devices, it was concluded that electronic conduction in these devices is dominated by an effective tunneling barrier width that varies with time under the applied voltage. Thus, the switching effect is primarily attributed to an effective tunneling distance modulation, which is in line with the present assumptions for the *Rt-L* dependence.

A heuristic equation  $L(V_M, t)$  that qualitatively gives the expected response of L as a function of the time t and the applied voltage  $V_M$  is given below:

$$L(V_M, t) = L_0 \cdot \left(1 - \frac{m}{r(V_M, t)}\right).$$

(2.5)

$L_0$  is the maximum value that *L* can attain. The term in parenthesis of Eq. 2.5, which contains a voltage-dependent parameter  $r(V_M, t)$  and a fitting constant parameter *m*, determines the boundaries of the barrier width. By considering tunneling as the dominant physical mechanism, Eq. 2.5 introduces the initial as well as the current position of *L* which is limited within two boundary values. Parameter  $r(V_M, t)$  defines both the device dynamics and the current state of the device. Its value is monitored and maintained within a valid range; i.e. when  $r < r_{MIN}$  or  $r > r_{MAX}$ , it is set equal to  $r_{MIN}$  or  $r_{MAX}$ , corresponding to  $L_{MIN}$  and  $L_{MAX} \approx L_0$ , respectively. As a consequence, the memristance is correspondingly set to the most ( $R_{ON}$ ) or the least

conductive state ( $R_{\text{OFF}}$ ) via Eq. 2.4. Values for parameters *m* and  $r_{\text{MIN}}$  should be selected so that the fraction ( $m/r_{\text{MIN}}$ ) < 1 (so, the tunnel barrier-width will never be zero).

Furthermore, since "set" and "reset" switching times can differ in many experimental memristive devices, this model is based on the assumption that the switching rate of *L* is small (fast) below (above) a threshold voltage ( $V_{\text{SET}}$  or  $V_{\text{RESET}}$ ), which is viewed as the minimum voltage required to impose a change on the physical structure, and thus the memristance, of the device. This assumption is encapsulated in the use of the voltage-dependent parameter  $r(V_M, t)$ , whose time derivative is slow or fast depending on the applied voltage, as shown below:

$$\dot{r}(V_M, t) = \begin{cases} a_{RESET} \cdot \frac{V_M + V_{RESET}}{c + |V_M + V_{RESET}|}, & V_M \in [-V_0, V_{RESET}) \\ b \cdot V_M, & V_M \in [V_{RESET}, V_{SET}] \\ a_{SET} \cdot \frac{V_M - V_{SET}}{c + |V_M - V_{SET}|}, & V_M \in (V_{SET}, +V_0] \end{cases}$$

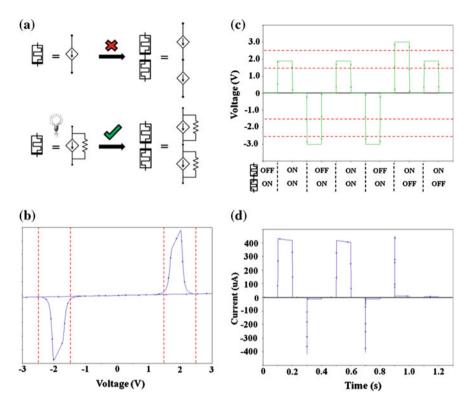

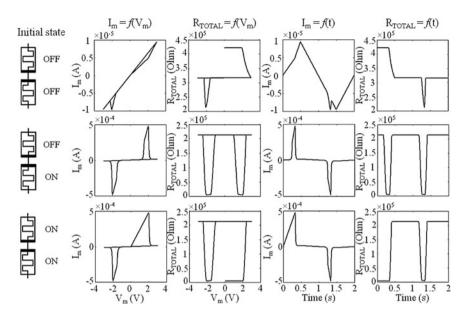

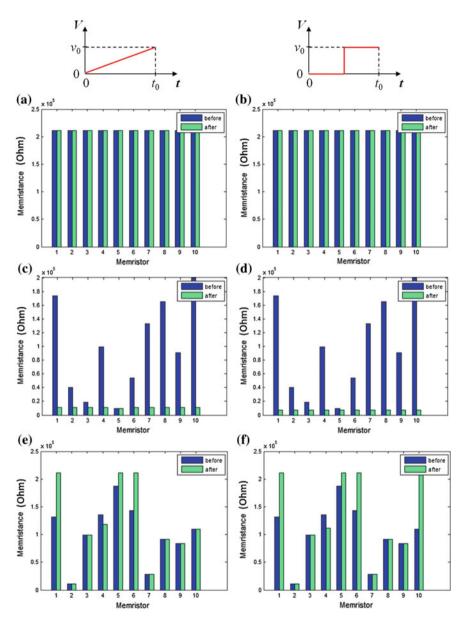

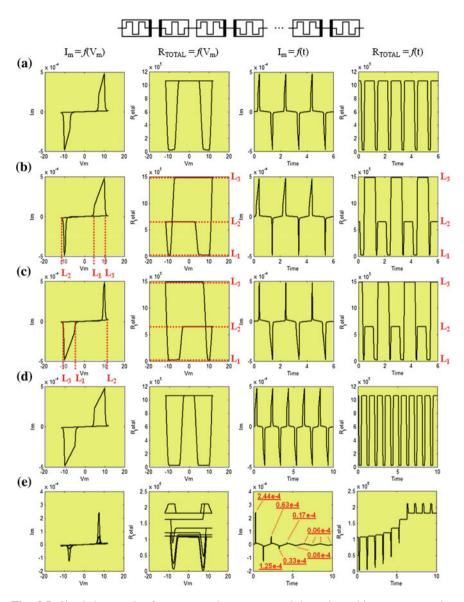

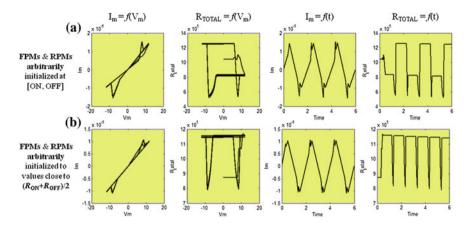

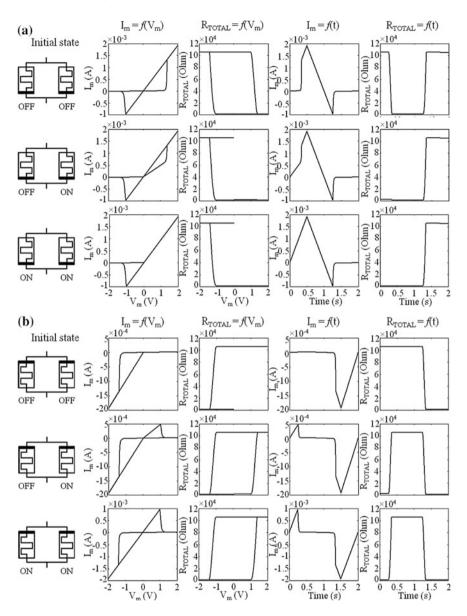

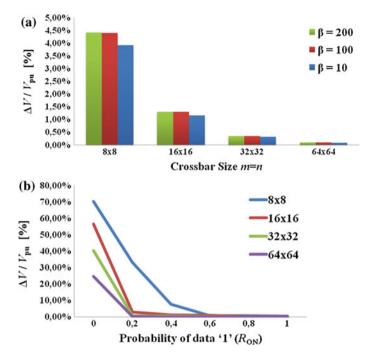

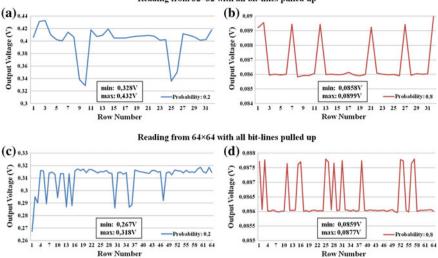

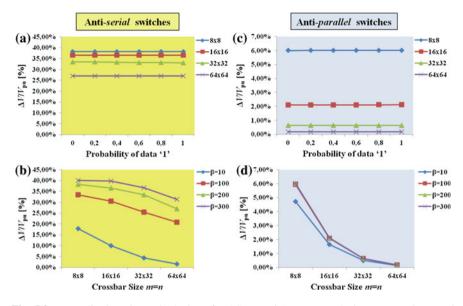

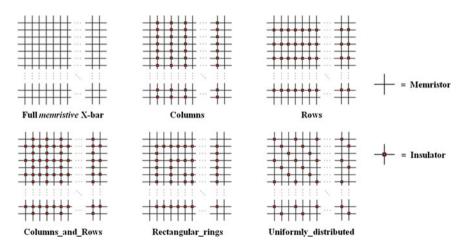

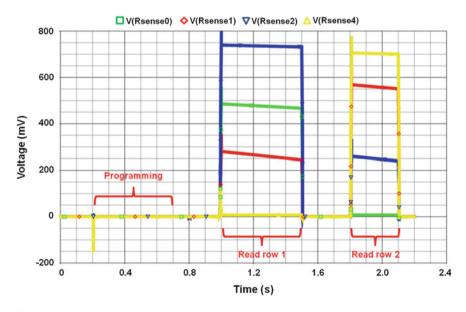

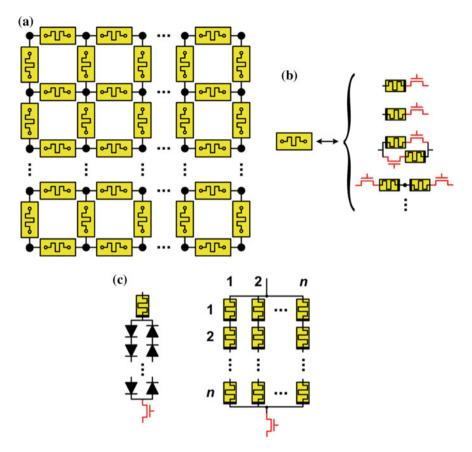

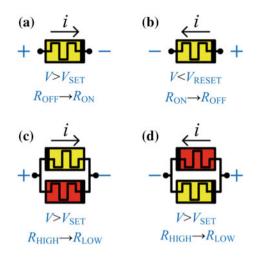

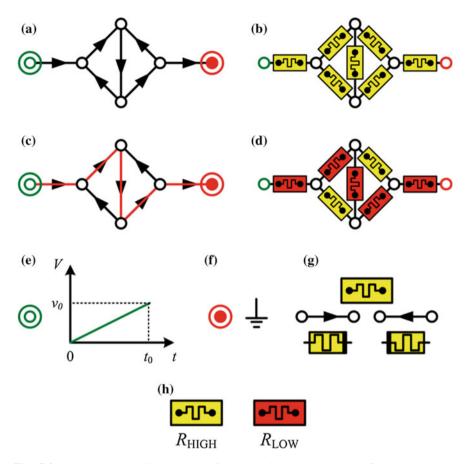

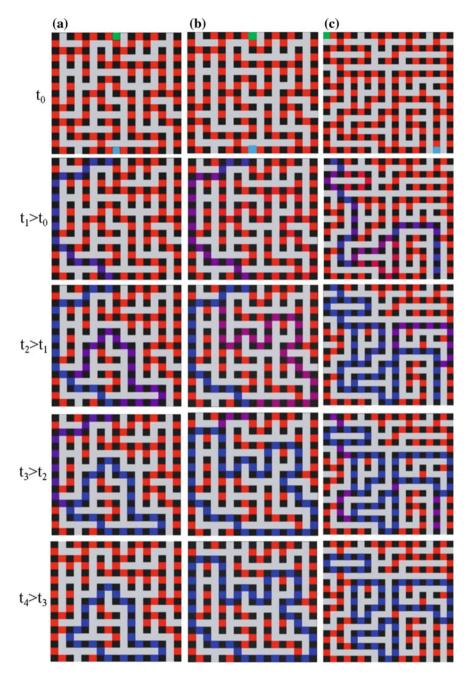

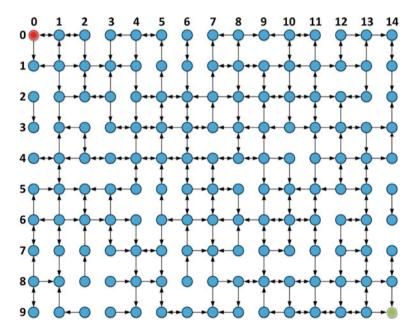

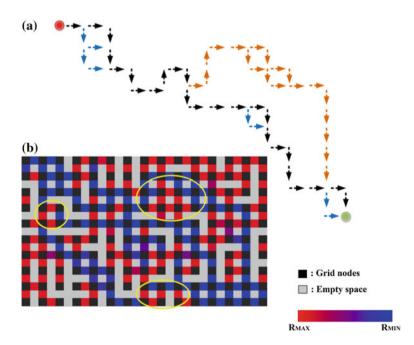

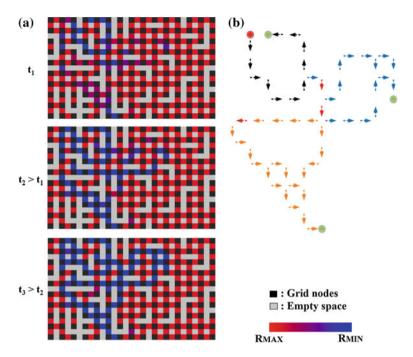

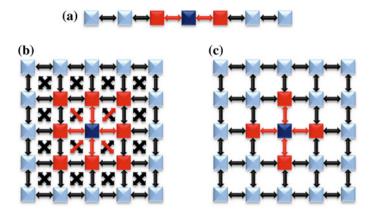

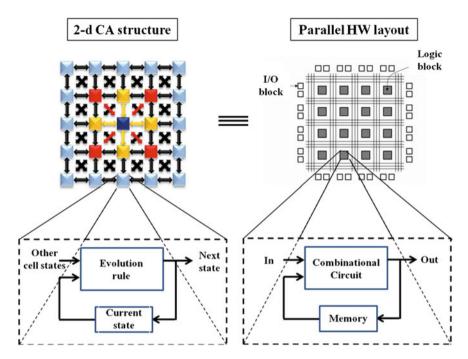

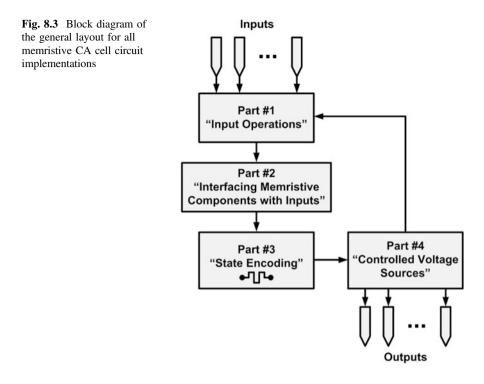

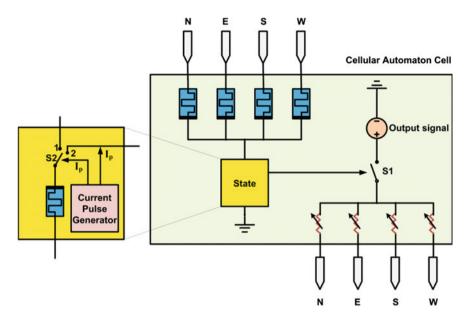

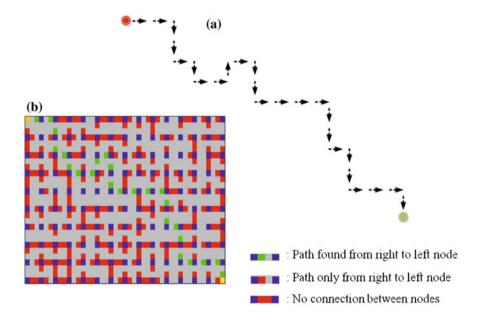

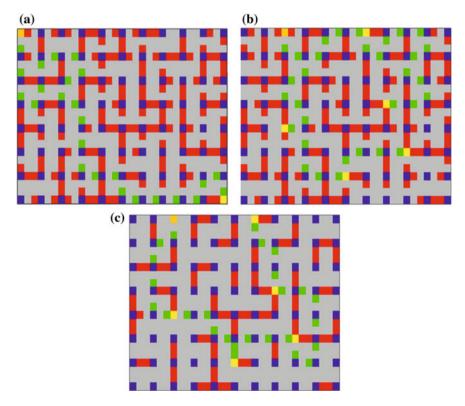

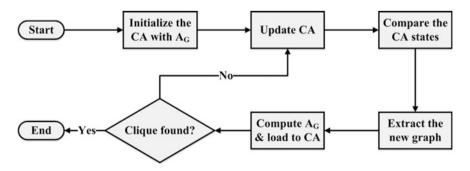

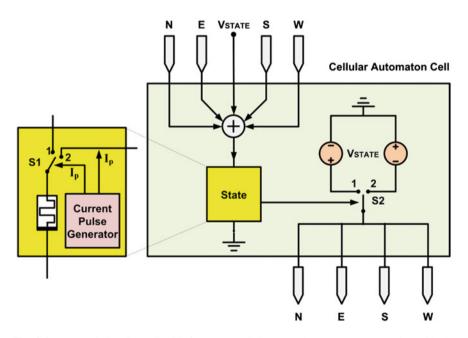

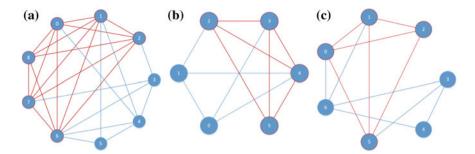

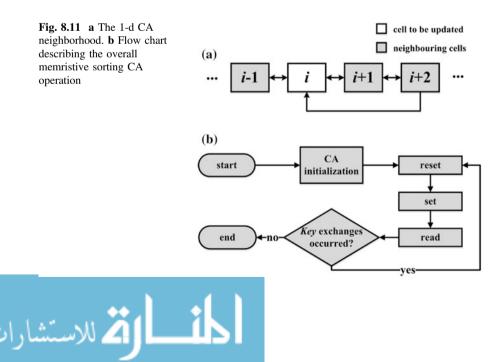

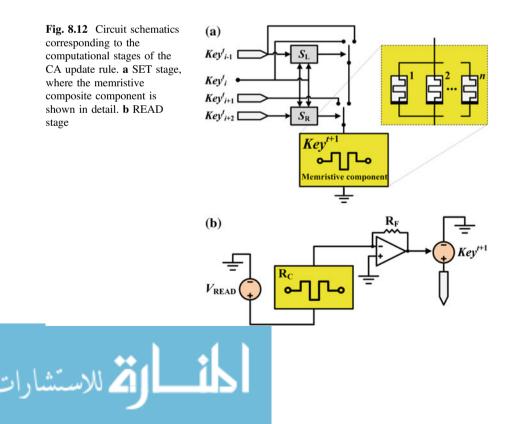

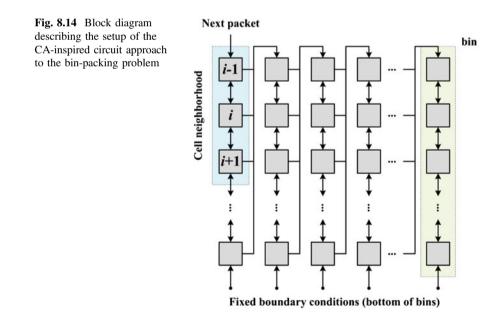

(2.6)